תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:11.

- שונה לאחרונה 2025-01-23 14:46.

בעבר כתבתי מדריך כיצד לבנות מחשב מבוסס Z80, ועיצבתי את המעגל כך שיהיה פשטני ככל האפשר, כך שניתן יהיה לבנות אותו כמה שיותר בקלות. כתבתי גם תוכנית קטנה תוך שימוש באותו רעיון של פשטות. העיצוב הזה עבד די טוב, אבל לא הייתי מרוצה ממנו לגמרי. התחלתי עם שכתוב תוכנה עבורה שאפשר לתכנת אותה בזמן ריצה. זה היה כדי לאפשר לי לבדוק פיסות קוד מבלי שאצטרך להקדיש אותו ל- EEPROM, מה שידרש ממני לתכנת מחדש את ה- EEPROM. זה לא נשמע לי כמו רעיון מהנה. ואז התחלתי לחשוב על מרחבי זיכרון. אם רציתי להתמקד בחתיכת חומרה (IO בעיקר), פיסת קוד עשויה לחרוג מכמות שטח הזיכרון העומדת לרשות המערכת. זכור, העיצוב השתמש רק בבייט התחתון של אוטובוס הכתובות ולאחר מכן נעשה שימוש בביט התחתון של הבייט הגבוה לבחירה בין רווחי ROM לבין רווחי זיכרון RAM. המשמעות הייתה שיש לי רק 253 בתים של שטח לשימוש. ייתכן שאתה שואל מדוע 253 במקום 256. הסיבה לכך היא שהקוד החדש שלי מזריק שלושה בתים של נתונים בסוף תוכנית כתובה (זה יכוסה מאוחר יותר, כיוון ששיניתי אותו לעבודה על העיצוב החדש).

נ

חזרתי על התרשימים הישנים שלי כדי לראות מה עוד קורה. מצאתי פגם קטן במעגל בחירת הזיכרון, אותו אכסה כשאגיע לשם. הגרסה הפשוטה: כל בקשות הכתיבה אכן היו עוברות, אם כי היא תמיד הוכנסה ל- RAM. זה כנראה לא היה משהו ששווה לדאוג לו, אבל רציתי לעשות את זה כמו שצריך הפעם. ועם זה התחלתי לצייר סכמטי חדש. שתי התמונות המצורפות לדף זה הן לפני ואחרי המעגל בפועל. ניקיתי כל כך הרבה מחוטי הספגטי, זה לא מצחיק.

נ

אם עקבת אחרי ההגשה המקורית שלי ומתכנן לעקוב אחר זה, אתה הולך לשנוא אותי. אם אתה מתחיל מחדש, אז יש לך מזל. פשוט תפוס את החלקים ברשימה (או המקבילה שלהם) ועקוב אחריהם.

אספקה:

LM7805 - רגולטור 5 וולט Z80 - המעבד; המוח של המערכת AT28C64B - EEPROM. אחסון נתונים "קבוע" המשמש לקושחת המחשב IDT6116SA - SRAM; משמש לאחסון קוד משתמש ו /או אחסון נתונים כללי NE555 - שעון מערכת 74HC374 - אוקטל D -Latch עם /OE; משמש כשבב הקלט74LS273 - אוקטל D -Latch עם /MR; שבב פלט TLC59211 - שבב מנהל התקן LED (בשימוש כך ש- 74LS273 יכול להניע נוריות LED, מכיוון שהוא לבדו אינו מסוגל לפלט הנוכחי) MC14572 - זהו שבב "מנהל התקן", אך מצאתי שהוא מושלם להגיון בקרת הזיכרון. יש לו 4 ממירים ושער NAND ו- NOR שנבנה in74LS32 - שער Quad ORCD4001 - שער Quad NORCD4040 - מונה אדוות 12 שלבים; מחלק שעונים מצויר, אך לא מיושם (להפעלת המערכת במהירויות שעון נמוכות יותר) 2 נגדים של 10K אוהם - אחד משמש במעגל הטיימר 555, אז השתמש בכל ערך שתרצה עבורו 4 נגדים של 1K אוהם - אחד משמש עבור מעגל טיימר 555, אז השתמש בכל מה שאתה רוצה בו. אחר משמש לנהיגה של נוריות LED, לכן יש לשנות אותו גם אם אתה רוצה 8x330 Ohm Resistor Bus8x10K Ohm Resistor Bus11 נוריות - שלוש משמשות למצב המערכת ושמונה האחרות הן יציאות. עבור 8, השתמשתי בתצוגת תרשים עמודות (HDSP -4836) 4 קבלים - שניים משמשים LM7805; 0.22uF ו- 0.1uF. האחד מיועד לטיימר 555, אז השתמש במה שאתה מרגיש שנכון. האחרון הוא לאיפוס ההפעלה; 100uF2 N. O. לחצני לחיצה - אחד משמש לקלט, השני לאיפוס 8 מתגי DPS SPST - קלט נתונים; השתמשתי ב- Piano Key styleWire. הרבה הרבה חוטים

נ

הערה: גרסת MC14572 דרך החור מיושנת, אך גרסת ה- SMD עדיין פעילה (אפילו לא סטטוס "לא לעיצוב חדש"), כך שתצטרך לרכוש לוח מעגלים כדי לאפשר לך להשתמש בו. ניתן להשתמש ב- 74LS32 שני במקום ה- MC14572 (עיין בתרשים של "מעגל בחירת זיכרון" של ible הקודם)

שלב 1: סקירה מהירה של שינויים + סכמטים

אופן קריאת התרשימים: חץ שהצביע לתוך שבב הוא קלט: קלט> -חץ המופנה הרחק משבב הוא פלט: פלט <-בוסים להשתמש בקו במקום בחץ: אוטובוס |-

נ

רוב הצ'יפס נמשכו בעזרת הסיכות המדויקות שלהם. הטבילה הקטנה נמשכה על השבבים האלה. ברוב השבבים יש גם מספרי סיכות ותוויות. יכול להיות שקצת קשה לקרוא אותם. העיפרון שלי נהיה משעמם.

נ

מבחינת חיבורי מעגלים, הפריסה של העיצוב החדש היא לרוב ללא שינוי מהמקור. חיברתי את הנשנוש התחתון של הבייט הגבוה בכתובת לזיכרונות ולאחר מכן השתמשתי בביט הנמוך של הנשנוש העליון (A12) לבחירת זיכרון RAM/ROM. המשמעות היא שחלל ה- ROM עבר מ- 0000-00FF עד ל- 0000-0FFF. מרחב ראם עבר מ- 0100-01FF ל- 1000-1FFF. החלפתי גם את לוגיקת בקרת הזיכרון לעיצוב טוב יותר והוספתי שני נוריות סטטוס חדשות (וקצת היגיון דבק). ציירתי (אך לא חיברתי) מעגל מחלק שעונים. זה היה אמור לבצע שתי פונקציות. הפונקציה הברורה היא לחלק את תדר השעון למטה. הפונקציה הנוספת מיועדת למטרות PWM (Pulse Width Modulation), מכיוון ש- 555 אינו מייצר גלים עם 50% מחזורי עבודה. זה לא ממש משנה במעגל הזה, אבל אם היית רוצה להשתמש בשעון כדי להניע כמה נוריות, בהחלט תבחין בהשפעות (אחד (סט) הלדים יהיה עמום יותר מהשני). שאר המעגלים ללא שינוי.

שלב 2: מעבד, זיכרון ושליטה בזיכרון

זה החלק שבו קוראי הגרסה הקודמת שלי שונאים אותי. במבנה המקורי, פשוט זרקתי חלקים על הלוח במקום שהם נראו כאילו הם יניבו בעיה קטנה עם החיבור. התוצאה נראתה כאילו מישהו זרק עליה צלחת ספגטי והייתה כמו "חוטים!" רציתי לנקות אותו מעט, אז התחלתי לקרוע הכל חוץ מהמעבד, ה- RAM וה- ROM. משכתי כמעט את כל מעגל הקלט, מעגל הפלט ואת היגיון הדבק. זה כמעט כאב לי לעשות, אבל זה היה הכרחי. השארתי את כל חיבורי הנתונים שלמים ואת הבייט התחתון של אוטובוס הכתובות. לאחר מכן חיברתי את ארבעת הביטים הבאים של אוטובוס הכתובות (A8-A11) לשבב ה- ROM. דאגתי לעקוף את השבב הפעם כדי להקל על המשיכה לתכנות מחדש. הקפצתי גם את חיבורי הכתובת לשבב ה- RAM.

נ

עם זה מהדרך, הייתי צריך עכשיו לחבר את ההיגיון של בקרת הזיכרון. בתרשים המקורי, חיברתי את קו המעבד /MREQ ישירות ל- /CE לשני שבבי הזיכרון, ואז חיברתי /WR ל- RAM /WE. לאחר מכן היו לי ה- CPU /RD ו /MREQ לוגי או OR יחד יחד כמו גם A9. בעיקרו של דבר, הוא הוגדר כך שכל בקשות הזיכרון הפעילו זיכרון RAM וגם ROM, אך A9 שימש לבחירת מי מהשבבים /OE שנבחרו. זה היה בסדר והכל מכיוון שהשבבים יישארו לא פעילים עד שתוגש בקשת זיכרון ואז רק אחד /OE יהיה פעיל במהלך בקשת קריאה. זה מנע דיון חוצה, אך הציג ניואנס מביך. מכיוון ש- A9 שימש רק לקביעת איזה שבב מוציא נתונים ומכיוון שלמעבד הייתה גישה ישירה לסיכת ה- RAM /WE, כל בקשת הכתיבה תעבור. זה היה בסדר עבור ה- ROM מכיוון שמצב הכתיבה שלו מעוכב על ידי קשירה /WE ישירות לאספקה של 5V. עם זאת, ה- RAM ייכתב ללא קשר ל- A9. המשמעות היא שניסיון כתיבה למיקום שטח ROM יכתוב לאותו מיקום במרחב RAM.

נ

פתרון אחד לכך יהיה חיווט מחדש של היגיון הבקרה כך שלמעבד תהיה גישה ישירה לסיכות השבבים /OE ו /WE ולאחר מכן באמצעות MREQ ו- A12 כדי לבחור אילו שבבים /CE מונעים. הלכתי עם הרעיון הזה, אבל במקום להשתמש בארבעה שערים של NOR ומהפך כמו העיצוב המקורי, מצאתי שבב קטן ומביך שהיה מושלם למשימה. הייתי צריך ליצור מעגל שהשתמש רק בשערי ההיגיון הזמינים בשבב, אבל זה היה קל מספיק. A12 ניזון ישירות לשער NAND ולשער NOR. /MREQ מוזנת לשער NOR ומחמאתו מוזנת לשער NAND. שער NAND משמש לכונן /CE עבור זיכרון ה- RAM ויציאת NOR הופכת והופכת את ROM /CE. זה הופך את זה ל /MREQ חייב להיות נמוך לפני שנבחר כל שבב ואז A12 בוחר איזה מהם ייבחר. עם התקנה זו, כעת כל בקשת כתיבה ל- ROM לא תעשה דבר. זה גם חוסך בחשמל כי רק שבב אחד פעיל במקום שניהם. באשר לשבב ההיגיון עצמו, עדיין יש לנו בפנים שני ממירים שאינם בשימוש. אחד יתרגל מאוחר יותר, אך נגיע לשם כשנגיע לשם.

שלב 3: נוריות מצב מערכת

לפני שהתחלתי בפרויקט הזה, ניסיתי להתממשק עם IC מסוים, אך התקשיתי עם זה. לא בטוח מה קורה, השתמשתי בלוח בעל הרכבה על הלוח כדי לחקור מסביב (אחד מאותם מכלולים עם הנגד מובנה). פעולה זו נתנה לי רעיון נוסטלגיה שעדיין משמש כיום: נוריות סטטוס המשמשות לציון אם קוראים או כותבים אליו זיכרון. זה היה אמור לשמש יחד עם נורית הקלט שכבר הייתה לי. נורית הקלט הייתה מחוברת למחולל האותות /WAIT כדי לציין לנו שהמערכת, ובכן, מחכה לקלט (אני אגיע לשם, אל תדאג). שקלתי להוסיף נורית לציון IO לכתוב, אבל הבנתי כי נוריות הפלט שמשתנות כבר יהיו אינדיקטור מצוין לכך. כשאני חושב על זה, אני עדיין יכול להוסיף את זה עדיין. עם זאת, אני מוצא את זה שימושי לדעת אם קוראים או כותבים זיכרון. ובכן, זה שימושי לניפוי באגים בתוכניות. למעשה השתמשתי בה ככזה כשניסיתי לגרום לתוכנית שלי לפעול: "למה היא כותבת לזיכרון? זה עדיין לא אמור לעשות את זה!"

נ

כדי לשלוט בנוריות אלה השתמשתי בשער ה- NOR המרובע. השתמשתי בכל השערים. רק שניים שימשו ליצירת אותות הסטטוס, אך לשבב אין יכולות כוח להניע את הנוריות בפועל. הם מסוגלים לשקוע כל כך הרבה כוח, אז השתמשתי בשני השערים האחרים של NOR כממירים וחיברתי את הנורות ככאלה. מכיוון שנורית אחת משמשת לציון קריאות והשנייה לכתיבה, ובקשה קריאה וכתיבה לא תופיע במקביל, הצלחתי להתחמק משימוש בנגד אחד בלבד עבור שני הלדים. באשר לאותות שהייתי צריך לפענח, זה גם היה קל מספיק. רציתי שכל בקשות קריאת הזיכרון יצוינו, כך שלשער NOR הראשון היו /MREQ ו /RD על הכניסות שלו. סטטוס הכתיבה היה קצת יותר מסובך, אבל קל באותה מידה. עדיין השתמשתי ב- /MREQ כקלט אחד, אך שימוש ב- /WR כשני יגרום לניואנס מינורי שרציתי להימנע ממנו. זה היה מציין את כל בקשות הכתיבה. רציתי רק את אלה שעברו בפועל. אז איך הייתי עושה את זה? ובכן, זוכר כיצד הגדרתי את המערכת כך שניתן לכתוב רק זיכרון RAM? השתמשתי ב- RAMs /CE כקלט השני לשער NOR. המשמעות היא שהנורית תדלק רק כאשר תיבחר זיכרון RAM ותתבקש בקשת כתיבה. מבחינת צבע הלד, בחרתי כתום כמחוון הקריאה (אך מצאתי רק צהוב) ואדום כמחוון הכתיבה.

שלב 4: קלט ופלט

בשלב הקודם, אולי שמת לב שהוספתי כבר חלק משאר הרכיבים ללוח. שמרתי את המקום כך שלא בטעות הייתי מניח חוטים היכן שרציתי רכיב (ולכן אצטרך למצוא מיקום חדש לרכיב האמור). אולי גם שמתם לב שהשארתי את מתגי הכניסה במקומם וחיבורתי למעקה החשמל. החלטתי שהמיקום המקורי הוא המקום המושלם והחלטתי למקם את נוריות הפלט בקרבת מקום (למעלה). מימין לתצוגת הבר נמצא תפס הכניסה. מעליו תפס הפלט, ומשמאלו נמצא מנהל ההתקן LED. התחלתי בחיבור הצג לנהג מכיוון שזה היה הכי קל לעשות. לאחר מכן חיברתי את המתגים לצד הכניסה של תפס הכניסה. לאחר מכן חיברתי את צד הפלט של תפס הפלט למנהל ההתקן LED. זה אולי נראה כמו פקודה מביכה לקבל את החוטים האלה, אבל זה היה מסיבה. הקלט של תפס היציאה אמור להיות מחובר לאוטובוס הנתונים כמו גם הפלט של תפס הכניסה. הרעיון היה לחבר את הפלט של תפס הכניסה לכניסות של תפס היציאה, מה שעשיתי. אז כל מה שהייתי צריך לעשות זה לחבר את הבלגן הזה לאוטובוס הנתונים. לא משנה לאן הקשרים הללו הלכו פיזית מכיוון שכולם יהיו מחוברים חשמלית. המחשב כמעט סייר כעת.

שלב 5: אפס וסיים קלט ופלט

מצטער, אין תמונות לשלב זה. עיין בשלב הקודם לתמונות.

נ

אולי שמתם לב בתמונה האחרונה של השלב הקודם, התקנתי כפתור ירוק ושבב לוגי נוסף. השבב הוא שער ה- OR. שני שערים משמשים ליצירת האות /WAIT. ובכן, אחד מייצר את האות על ידי OR-ing /IORQ ו /RD מהמעבד. הפלט מוזר לשער השני, שם הוא מקבל OR OR שוב ללחצן לחיצה. הכפתור מעלה את קלט השער גבוה, ובכך מעלה את הפלט גבוה. פלט זה מוזן למעבדים /סיכת WAIT. בעוד שהוא לא נלחץ, הנגד שומר את הקלט נמוך. בתחילה השתמשתי בנגד 10K, אך ה- LS32 למעשה הוציא מתח על הכניסה. הנגד לא הוריד אותו מספיק נמוך והייתי צריך להחליף אותו ב- 1K. בכל אופן, הרעיון הוא שכאשר מתבצעת בקשת קריאה של IO, השער הראשון והשני של OR אומר למעבד לחכות. לאחר שתגדיר את מתגי הכניסה למה שאתה רוצה, אתה לוחץ על הכפתור וזה מוציא את המעבד ממצב ההמתנה. נורית ה"קלט "הירוקה, כפי שקראתי לה בשלב מוקדם יותר, מחוברת כך שכאשר סיכה /WAIT יורדת, היא נדלקת.

נ

אבל עדיין לא סיימנו. כפוף הכניסה זקוק לאות כדי ליידע אותו כאשר קלט הנתונים תקף ויש להוציא אותו למעבד. סיכת השעון הזו פעילה גבוה. לפני כן, פשוט חיברנו אותו לכפתור. זו עדיין אפשרות תקפה, אך הפעם בחרתי לשים אותה על אותו פלט כמו שער ה- OR השני. ל- IC זה יש גם סיכה /OE שצריך להניע. אם הוא היה נשמר גבוה, הוא לעולם לא היה מוסיף נתונים לאוטובוס. אם זה היה נמוך, זה תמיד היה נהיגה באוטובוס. כדי לתקן זאת, פשוט השתמשתי בשער OR שלישי. הכניסות הן /IORQ ו /RD והפלט עובר ישירות לתפקיד ה- OE /הבריח.

נ

תפס הפלט זקוק גם לנעילת סיכת השעון. שוב, הוא פעיל גבוה. בסכימה שלי ציירתי את שער ה- OR הרביעי ישירות שהניע את הסיכה באמצעות /IORQ ו /WR. המשמעות היא שסיכת השעון תישאר גבוהה עד שתוגש בקשת כתיבה, ואז היא תרד ואז תהיה גבוהה יותר. זה כנראה היה בסדר מכיוון שלאוטובוס הנתונים עדיין היו נתונים תקפים עליו מיד לאחר ניסיון הכתיבה, אך מבחינה הנדסית היה עיצוב אשפה. לא שמתי לב לשגיאה זו רק לאחר שצילמתי את התמונות הסופיות, אבל ניסיתי לחבר את החיבור הזה ואז הזנתי את פלט השער OR לאחד הממירים שאינם בשימוש מהיגיון בקרת הזיכרון, ואז חיברתי את הפלט שלו לסיכת השעון.. תיקנתי גם את הסכימה ומצאתי שגיאה נוספת שעשיתי. תיקנתי גם את זה.

נ

עם כל זה סוף סוף, הייתה לי כמות קטנה מאוד של עבודה: מעגל האיפוס. הוספתי כפתור ללוח והשתמשתי בנגד 10K כדי להחזיק צד אחד גבוה. הצד השני עובר ישירות לקרקע. הצד הגבוה הוא הפלט /RESET, שהגיע לכל שבב עם סיכה /RESET (המעבד ותפס הפלט). כדי לבצע איפוס הפעלה, הוספתי קבל ליציאה /RESET. הרעיון הוא שמנגד הערך הגדול יגרום לקבל הגדול יחסית להיטען לאט ולהחזיק את סיכות /RESET נמוכות במשך כמות מסוימת של מחזורי שעון (המעבד זקוק לארבעה מחזורי שעון). אתה בטח כבר יכול לנחש מה הצד השלילי של המעגל הזה. זה אותו שלילי כמו הגרסה הקודמת מכיוון שזה אותו מעגל. כאשר לוחצים על הכפתור, הקבל בעצם מקוצר דרך הכפתור. זה רע הן למכסה והן לכפתור, כך שאם אתה רוצה להפוך את המבנה שלך לקבוע קצת יותר, ייתכן שתרצה לעצב אותו מחדש. חשבתי על עוד 555 טיימר שיוצב במצב חד -יציב. אך עם זאת, מעגל המחשבים הסתיים כעת. יש. עכשיו זה צריך להיות מתוכנת.

שלב 6: תכנות

לתכנת את הדבר הזה היה סיוט. בניתי מתכנת Arduino EEPROM. זה לא עבד. בניתי עוד אחד המבוסס על עיצוב וקידוד של מישהו אחר. עדיין לא עבד. חזרתי לשיטה המומלצת של הגדרה ידנית של הכתובות ותאי הנתונים. איכשהו, פישלתי את זה. ניסיתי שוב ועדיין טעיתי. חזרתי שוב וגיליתי שזה כבוי בבת אחת, אז תיקנתי את זה וזה סוף סוף עבד, תודה לאל.

נ

באשר לתוכנית בפועל, נראה שהיא סופר מורכבת וקשה לעקוב אחריה, אך היא לא. זה די פשוט, למעשה. חצי מזה מעתיק מספרים מסביב. החצי השני חולק בין מתמטיקה של 16 סיביות, קפיצות מותנות, ועם זאת עוד יותר העתקת מספרים מסביב. אז תן לי לעבור על זה ולספר לך איך זה עובד.

נ

האתחול קובע רק כמה ערכי רישום לשימוש התוכנית. לולאת התוכניות קצת יותר מורכבת, אבל לא הרבה. ראשית, הוא מקבל קלט לרשם A ביציאה 00. לאחר מכן נרשם ה- E נכתב בזיכרון. בשתי הלולאות הראשונות, מאגר ה- E מכיל נתוני זבל, ולכן אנו מנסים לכתוב אותו לשני הבייטים האחרונים של שטח ROM מכיוון שהם לא ייכתבו בפועל; מצביע הכתובת (IY) מצטבר לאחר מכן. הערך המאוחסן ב- D מועבר לאחר מכן ל- E כדי להיכתב לאחר מכן. A נטען לאחר מכן ל- D ו- L ו- E מועתקים ל- H. HL הוא המקום בו השוואת הערכים מתבצעת באמצעות חיסור ובדיקת ZF (דגל אפס). הערך הראשון לעומת זה מאוחסן ברשומות B ו- C. B ו- C מטופלים כרשם יחיד של 16 סיביות, BC. אם הערכים זהים, התוכנית קופצת היישר לחלל ה- RAM, שם מניחים שקוד המשתמש יושב. אם הקוד ב- BC אינו התאמה, אז HL נטען מחדש עם הערכים ההתחלתיים מ- D ו- E ונשווה שוב לערך ב- SP באותו אופן שבו הושווה ל- BC. אם מדובר בהתאמה, יש לה אותה תוצאה, אבל שלושה בתים נוספים נכתבים בזיכרון. הבייטים הם קוד שגורם למעבד לקפוץ חזרה לתחילת התוכנית שלו (איפוס תוכנה). אולם אם ההשוואה השנייה לא הייתה התאמה, התוכנית לולאת למקום שבו היא תופסת ערך מהמשתמש.

נ

LD SP, EDBFH; קוד exe (מוסיף קפיצה)

נ

LD IY, FFEH; מצביע זיכרון ראשוני לאחסון קוד

נ

LD BC, EDC3H; קוד exe (ללא לולאה)

נ

לולאה; הוראת assembler כך שלא נצטרך לדעת היכן נמצא החלק הזה בזיכרון

נ

ב- A, (00H); לקבל נתוני התוכנית

נ

LD (IY+00H), E; E מכיל קוד לאחסון

נ

INC IY; עבור למיקום הזיכרון הבא

נ

LD E, D; ld D לתוך E

נ

LD D, A; ld A לתוך D

נ

LD H, E; l E לתוך H

נ

LD L, D; ld D לתוך L.

נ

או א; אפס את דגל הנשיאה

נ

SBC HL, BC; מחזיר 0 אם הוזן קוד exe 2

נ

JP Z, 1000H; אם כן, קפוץ ותבצע תוכנית

נ

LD H, E; אחרת, רענן אותם לערכים מתאימים

נ

LD L, D.

נ

או א; החסר הראשון עשוי להגדיר את דגל הנשיאה. תנקה את זה

נ

SBC HL, SP; מחזירה 0 אם הוזן קוד exe 1

נ

JP NZ, לולאה; אם לא, חזור על התהליך (מתחיל בקבלת ערך)

נ

LD (IY+00H), C3H; אחרת, הזן קוד קפיצה בסוף תוכנית המשתמש

נ

LD (IY+01H), 00H; קפיצה בעצם פועלת כאיפוס תוכנה

נ

LD (IY+02H), 00H; זה איפוס מלא במקרה שהרשמים ישתנו

נ

JP 1000H; לקפוץ ולבצע תוכנית משתמש

מוּמלָץ:

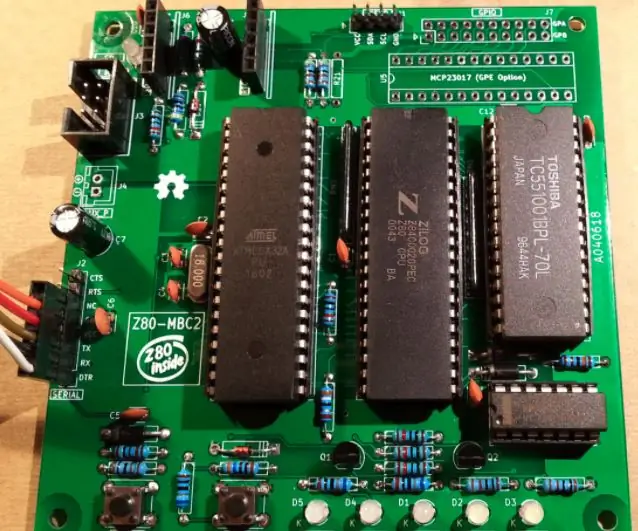

Z80 MBC2 - הידור מחדש של ביוס ומטען QP/M: 6 שלבים

Z80 MBC2 - הידור מחדש של ביוס ומטען של QP/M: אם כמוך אתה מוצא את עצמך במצב שבו אתה צריך לאסוף מחדש את ה- bio של QP/M עבור MBC2 שלך - כך אתה עושה זאת. תיעדתי התהליך, כיצד לאסוף מחדש את הגרסה הקיימת. זה תלוי בך לבצע שינויים בביוס בפועל

Z80 MBC2 - הידור מחדש של CPM2.2 Bios: 4 שלבים

Z80 MBC2 - הידור מחדש של CPM2.2 Bios: אם, כמוני, אתה מוצא את עצמך במצב שבו אתה צריך לאסוף מחדש את ה- bios של CP/M (2.2) עבור MBC2 שלך - כך אתה עושה זאת. במקרה שלי רציתי להסיר את הודעת "WARM BOOT" בכל פעם שקיימת תוכנית או כשעשית ctrl-c. אני א

דרכים מגניבות לשימוש מחדש בחלקי מחשב ישנים: 7 שלבים (עם תמונות)

דרכים מגניבות לשימוש מחדש בחלקי מחשב ישנים: במדריך זה אתן לכם בקצרה כמה רעיונות כיצד לעשות שימוש חוזר בחלקים מסוימים של מחשבים ישנים שכולם זורקים. אתם לא תאמינו, אבל במחשבים הישנים האלה יש חלקים מעניינים בפנים. לא ייתן מלא

מסגרת תצוגה של מחשב נייד מתוכנן מחדש: 6 שלבים (עם תמונות)

מסגרת תצוגת מחשב נייד מעוצב מחדש: כאשר המחשב הנייד הישן שלי סוף סוף מת, לא רציתי שכל הרכיבים הפונקציונליים לחלוטין יתמלאו להטמנה. לכן, הצלתי את לוח ה- LCD ובניתי מסגרת עץ פשוטה שתחזיק אותו כצג עצמאי. עיצבתי את המוצר הזה

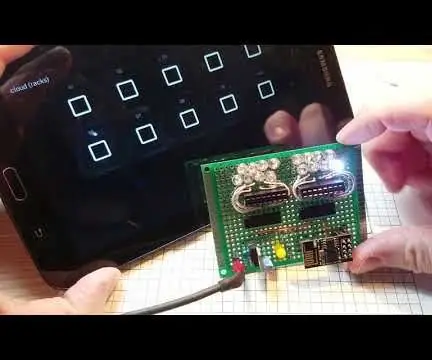

כיבוי מרחוק או הפעלה מחדש של מחשב באמצעות מכשיר ESP8266: 10 שלבים (עם תמונות)

כיבוי מרחוק או הפעלה מחדש של מחשב באמצעות מכשיר ESP8266: כדי שיהיה ברור כאן, אנו סוגרים את המחשב שלך, לא מחשב של מישהו אחר. חבורה של מתמטיקה, אבל כל בוקר בשעה 3 לפנות בוקר הם ננעלים. S