תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:14.

- שונה לאחרונה 2025-01-23 14:46.

בהוראה הקודמת שלי ראינו כיצד לעצב בקר מטמון ישיר ממופה. הפעם, אנו מתקדמים צעד קדימה. אנו נעצב בקר מטמון אסוציאטיבי פשוט בארבע כיוונים. יתרון ? שיעור החמצה פחות, אך במחיר הביצועים. בדומה לבלוג הקודם שלי, היינו מתכננים ומחקים מעבד שלם, זיכרון ראשי וסביבת מטמון כדי לבדוק את בקר המטמון שלנו. אני מקווה שאתם מוצאים זאת כהפניה שימושית להבנת המושגים ולעיצוב בקרי המטמון שלכם בעתיד. מכיוון שהדגם של המעבד (ספסל הבדיקה) ומערכת הזיכרון הראשית זהים לחלוטין לבלוג הקודם שלי, לא אסביר אותם שוב. עיין בפרק ההוראות הקודם לפרטים לגביו.

שלב 1: מפרטים

מבט מהיר דרך המפרט של בקר המטמון המוצג כאן:

- בקר מטמון אסוציאטיבי מארבע כיוונים (עבור לקישור זה אם אתה מחפש בקר מטמון ישיר).

- מטמון חד-בנקאי וחוסם.

- מדיניות כתיבה על להיטי כתיבה.

- מדיניות כתיבה סביב החמצות כתיבה.

- מדיניות החלפת עץ Pseudo-LRU (pLRU).

- מערך תיוג בתוך הבקר.

- פרמטרים הניתנים להגדרה.

מפרט ברירת המחדל של זיכרון המטמון והזיכרון הראשי זהים למדריך הקודם שלי. אנא התייחס אליהם.

שלב 2: תצוגת RTL של המערכת כולה

ייצוג RTL מלא של המודול העליון מוצג באיור (לא כולל המעבד). מפרטי ברירת המחדל של האוטובוסים הם:

- כל אוטובוסי הנתונים הם אוטובוסים של 32 סיביות.

- אוטובוס כתובת = אוטובוס 32 סיביות (אך ניתן להזמין כאן רק 10 סיביות לפי הזיכרון).

- בלוק נתונים = 128 סיביות (אוטובוס רחב רוחב לקריאה).

- כל הרכיבים מונעים על ידי אותו שעון.

שלב 3: תוצאות הבדיקה

המודול העליון נבדק באמצעות ספסל בדיקה, המדגם פשוט מעבד שאינו צינורי, בדיוק כמו שעשינו בהוראה האחרונה. ספסל הבדיקה יוצר בקשות נתוני קריאה/כתיבה לזיכרון לעתים קרובות. זה לועג להוראות טיפוסיות של "Load" ו- "Store", הנפוצות בכל התוכניות המבוצעות על ידי מעבד.

תוצאות הבדיקה אימתו בהצלחה את הפונקציונליות של בקר המטמון. להלן נתוני הבדיקה שנצפו:

- כל האותות קריאה/כתיבה של החמצה ופגיעה נוצרו בצורה נכונה.

- כל פעולות קריאת/כתיבת הנתונים הצליחו בארבע הדרכים.

- אלגוריתם pLRU אומת בהצלחה להחלפת קווי מטמון.

- לא זוהו בעיות חוסר עקביות/עקביות בנתונים.

- העיצוב אומץ בהצלחה לתזמון עבור מקסימום. תדירות הפעולה של השעון = 100 מגהרץ בלוח Xilinx Virtex-4 ML-403 (מערכת שלמה), 110 מגהרץ לבקר מטמון בלבד.

- זיכרונות בלוק הוסקו עבור הזיכרון הראשי. כל המערכים האחרים יושמו על LUTs.

שלב 4: קבצים מצורפים

הקבצים הבאים מצורפים כאן עם הבלוג הזה:

- קבצי VHD של בקר מטמון, מערך נתוני מטמון, מערכת זיכרון ראשית.

- מבחן ביצועים.

- תיעוד על בקר המטמון.

הערות:

- עיין בתיעוד להבנה מלאה של המפרטים של בקר המטמון המוצג כאן.

- כל שינויים בקוד תלויים במודולים אחרים. לכן, השינויים צריכים להיעשות בשיקול דעת.

- שימו לב לכל ההערות והכותרות שנתתי.

- אם מסיבה כלשהי, לא ניתן להסיק זיכרון RAM לחסימה עבור הזיכרון הראשי, הפחת את גודל הזיכרון, ואחריו שינויים ברוחבי אוטובוס הכתובות על פני הקבצים וכן הלאה. כך שניתן ליישם את אותו הזיכרון ב- LUT או ב- RAM מבוזר. זה יחסוך את זמן הניתוב והמשאבים. לחלופין, עבור אל תיעוד ה- FPGA הספציפי ומצא את הקוד התואם לבלוק RAM וערוך את הקוד בהתאם, והשתמש באותו מפרטי רוחב אוטובוס כתובת. אותה טכניקה עבור FPGA של Altera.

מוּמלָץ:

בקר Arduino רמזור באמצעות LED RBG - 4 כיוונים: 3 שלבים

בקר Arduino רמזור באמצעות LED RBG | 4 כיוונים: בפוסט זה אתה הולך ללמוד כיצד להכין בקר רמזור ארדואינו. בקר רמזור זה ישמש לבקרת זרימת התעבורה. ניתן ליישם אותם באזורים בעלי תנועה רבה כדי למנוע חסימות או תאונות תנועה

בקר רמזור Arduino - 4 כיוונים: 3 שלבים

בקר רמזור Arduino | 4 כיוונים: בפוסט זה אתה הולך ללמוד כיצד להכין בקר רמזור ארדואינו. בקר רמזור זה ישמש לבקרת זרימת התנועה. אלה יכולים להיות מיושמים באזורים בעלי תנועה רבה כדי למנוע חסימות תנועה או תאונות

שעון ניקסי עם ארדואינו - עיצוב פשוט ביותר: 4 שלבים

שעון ניקסי עם ארדואינו | עיצוב פשוט ביותר: לאחר יום עבודה ארוך, סוף סוף הצלחתי לייצר שעון ניקסי עם ארדואינו ושבב בידוד אופטי, אין צורך בדרייבר של ניקסי שקשה לרכוש אותו

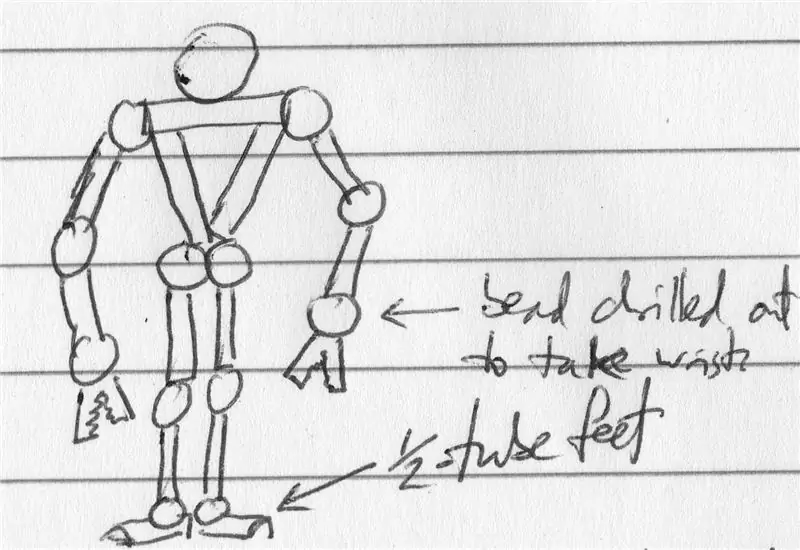

רובוט הזכוכית בארבע לפנות בוקר: 8 שלבים (עם תמונות)

רובוט הזכוכית בארבע לפנות בוקר: כמה אנשים שאלו אותי מאיפה אני משיג את הרעיונות שלי. אני לא בטוח, אבל אני יודע מתי אני מקבל אותם. אני לא יודע למה, אבל נראה שאני מקבל הרבה מהרעיונות שלי בזמנים לא נוחים - באמצע השיעור, הליכה הביתה בחושך, או, לעתים קרובות, אני מתעורר ב

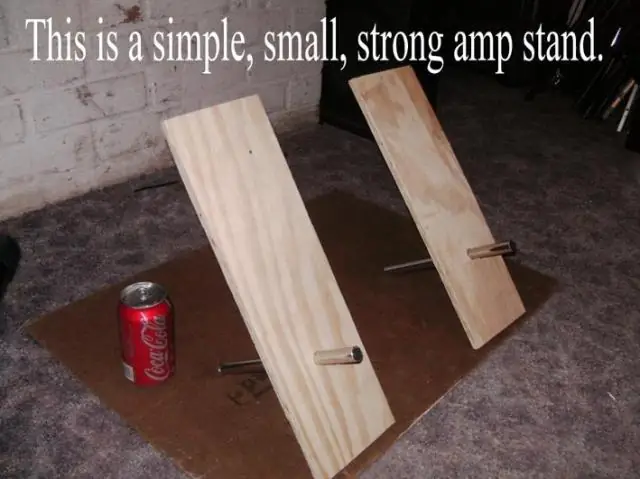

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: 9 שלבים

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: מעמד הטיה למגבר גיטרה - קל מדי - פשוט, קטן, חזק, חינם או ממש זול. לכל אמפר בכל גודל, אפילו ארונות גדולים עם ראש נפרד. פשוט צור לוחות וצינורות בגודל ואתה צריך כמעט לכל ציוד שאתה רוצה