תוכן עניינים:

- שלב 1: מהו Vivado HLS?

- שלב 2: ספריית הווידאו HLS

- שלב 3: סינתזה

- שלב 4: גרסאות ומידע אחר לייצוא

- שלב 5: ייצוא לספריית IP של Vivado

- שלב 6: ניתוח סינתזה וייצוא

- שלב 7: הוספת ספריית ה- IP ב- Vivado

- שלב 8: ביצוע שדרוג

- שלב 9: פרטים נוספים ומידע

- שלב 10: פלט וקלט

- שלב 11: ממשק רישום AXI

- שלב 12: פרגמה של Dataflow

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:17.

- שונה לאחרונה 2025-01-23 14:46.

האם אי פעם רצית לעבד בזמן אמת בוידאו מבלי להוסיף חביון רב או במערכת מוטבעת? לפעמים משתמשים ב- FPGAs (מערכי שער לתכנות שדות) לשם כך; עם זאת, כתיבת אלגוריתמים לעיבוד וידאו בשפות מפרט חומרה כמו VHDL או Verilog מתסכלת במקרה הטוב. הזן את Vivado HLS, הכלי Xilinx המאפשר לך לתכנת בסביבת C ++ וליצור ממנו קוד שפת מפרט חומרה.

תוכנות חובה:

- Vivado HLS

- ויוואדו

- (אם אתה משתמש ברשמי AXI) Vivado SDK

(אופציונלי) הורד את הדוגמאות של Xilinx כאן:

דוגמאות וידאו של Xilinx HLS

שלב 1: מהו Vivado HLS?

Vivado HLS הוא כלי המשמש להפיכת קוד דמוי c ++ למבני חומרה הניתנים ליישום ב- FPGA. הוא כולל IDE לביצוע פיתוח זה. לאחר שסיימת את פיתוח הקוד של HLS תוכל לייצא את ה- IP שנוצר שלך בפורמט לשימוש עם Vivado.

הורד את הקבצים המצורפים ושם אותם ליד המקום שבו תיצור את הפרויקט שלך. (שנה אותם בחזרה ל "top.cpp" ו- "top.h" אם יש להם שם אקראי)

שלב 2: ספריית הווידאו HLS

ספריית הווידאו של HLS כוללת תיעוד עם עיצובים הפניה במאמר זה: XAPP1167 משאב טוב נוסף הוא דף הוויקי של Xilinx בנושא.

התחל את Vivado HLS.

צור פרויקט חדש.

קח את הקבצים שהורדת בשלב הקודם והוסף אותם כקבצי מקור. (הערה: הקבצים אינם מועתקים לפרויקט, אלא נשארים היכן שהם נמצאים)

לאחר מכן השתמש בלחצן עיון כדי לבחור בפונקציה העליונה.

בעמוד הבא, בחר את החלק Xilinx שבו אתה משתמש.

שלב 3: סינתזה

פתרון => הפעלה סינתזה => פתרון פעיל

לאחר ~ 227.218 שניות, יש לבצע זאת. (הערה: זמן הסינתזה האמיתי שלך ישתנה בהתאם לגורמים רבים)

שלב 4: גרסאות ומידע אחר לייצוא

מספרי גרסאות מתקשרים עם Vivado כדי לגרום לך להיות מסוגל לעדכן את ה- IP בעיצוב. אם מדובר בשינוי גרסה מינורי ניתן לעשות זאת במקום, בעוד ששינויי גירסה גדולים דורשים להוסיף ידנית את הבלוק החדש ולהסיר את הישן. אם הממשקים שלך לא השתנו ועדכון הגרסה הוא מינור ניתן לעדכן את העדכון. נעשה באופן אוטומטי לחלוטין על ידי לחיצה על כפתור העדכון IP. תוכל להריץ "report_ip_status" במסוף tcl של Vivado כדי לראות את סטטוס ה- IP שלך.

הגדר את מספרי הגרסה ומידע אחר בפתרון => הגדרות פתרון …

לחלופין, ניתן להגדיר הגדרות אלה במהלך הייצוא.

שלב 5: ייצוא לספריית IP של Vivado

פתרון => ייצוא RTL

אם לא הגדרת את פרטי ספריית ה- IP בשלב הקודם, תוכל לעשות זאת כעת.

שלב 6: ניתוח סינתזה וייצוא

במסך זה אנו יכולים לראות את הנתונים הסטטיסטיים לגבי המודול המיוצא שלנו, המראים שהוא אכן עומד בתקופת השעון שלנו ב- 10ns (100MHz) וכמה מכל משאב הוא משתמש.

עם שילוב זה, דו ח הסינתזה שלנו וניתוח זרימת הנתונים שלנו, אנו יכולים לראות שהוא לוקח 317338 מחזורי שעון * תקופת שעון של 10ns * 14 שלבי צינור = 0.04442732 שניות. המשמעות היא שהחביון הכולל שנוסף על ידי עיבוד התמונה שלנו הוא פחות מעשרים שנייה (כאשר הוא משוער על 100MHz הממוקד).

שלב 7: הוספת ספריית ה- IP ב- Vivado

כדי להשתמש בבלוק ה- IP המסונתז שלך, תצטרך להוסיף אותו ל- Vivado.

ב- Vivado הוסף מאגר IP לפרויקט שלך על ידי מעבר לקטלוג ה- IP ולחץ באמצעות לחצן העכבר הימני על "הוסף מאגר …"

נווט לספריית הפרויקטים של Vivado HLS ובחר את ספריית הפתרונות שלך.

עליו לדווח על כתובת ה- IP שמצאה.

שלב 8: ביצוע שדרוג

לפעמים אתה צריך לבצע שינויים בלוק HLS שלך לאחר הכללתו בעיצוב Vivado.

לשם כך, באפשרותך לבצע את השינויים ולסנתז מחדש ולייצא את ה- IP עם מספר גרסה גבוה יותר (ראה פרטים בשלב מוקדם יותר אודות שינויים גדולים/קטנים בגירסאות).

לאחר שינוי ייצוא הגרסה החדשה, רענן את מאגרי ה- IP שלך ב- Vivado. ניתן לעשות זאת כאשר Vivado מבחין ש- IP השתנה במאגר, או מופעל באופן ידני. (שים לב, אם אתה מרענן את מאגרי ה- IP שלך לאחר ההתחלה, אך לפני שהייצוא מסתיים ב- HLS, ה- IP לא יהיה שם באופן זמני, המתן עד שיסתיים ותרענן שוב.)

בשלב זה אמור להופיע חלון עם המידע ש- IP שונה על הדיסק ונותן לך את האפשרות לעדכן אותו באמצעות כפתור "שדרוג שנבחר". אם השינוי היה שינוי גרסה מינורי ואף אחד מהממשקים לא השתנה, לאחר מכן לחיצה על כפתור זה תחליף אוטומטית את ה- IP הישן בחדש, אחרת עשויה להידרש עבודה נוספת.

שלב 9: פרטים נוספים ומידע

השלבים הבאים מספקים מידע נוסף על אופן הפעולה של סינתזת HLS ומה אתה יכול לעשות עם זה.

לקבלת דוגמה לפרויקט באמצעות בלוק IP מסונתז HLS, ראה הוראה זו.

שלב 10: פלט וקלט

יציאות ותשומות לבלוק ה- IP הסופי נקבעות מניתוח שעושה הסינתיסייזר של זרימת הנתונים פנימה והחוצה מהפונקציה העליונה.

בדומה ל- VHDL או verilog, HLS מאפשר לך לציין פרטים אודות החיבורים בין IP. שורות אלו הן דוגמאות לכך:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE ציר ציר = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE ציר ציר = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14 #pragma HLS INTERFACE = port_set

אתה יכול לראות כיצד היציאות המוצגות על בלוק ה- IP מושפעות מהנחיות אלה.

שלב 11: ממשק רישום AXI

על מנת לקבל קלט/פלט אל/מגוש ה- IP שלך ל- PS הדרך הטובה לעשות זאת היא באמצעות ממשק AXI.

אתה יכול לציין זאת בקוד HLS שלך, כולל הקיזוזים שישמשו אותם כדי לגשת לערך מאוחר יותר כך:

void image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = offset CONTROL_BUS = 0x1C #זרימת נתונים של HLS פרגמה

x = 42;

y = 0xDEADBEEF; }

לאחר חיבור תקין ב- Vivado, תוכל לגשת לערכים באמצעות קוד זה ב- Vivado SDK:

#include "parameters.h"

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

זה יגרום לך להגיע ל- 42 x ו- 0xdeadbeef ב- y

שלב 12: פרגמה של Dataflow

בתוך ה- DATAFLOW של #pragma משתנה האופן שבו הקוד מיושם מ- C ++ רגיל. הקוד בצנרת כך שכל ההנחיות פועלות בכל עת בחלקים שונים של הנתונים (תחשוב על זה כמו קו הרכבה במפעל, כל תחנה פועלת באופן רציף ומבצעת פונקציה אחת ומעבירה אותה לתחנה הבאה)

מהתמונה אתה יכול לראות שכל אחת מההנחיות

למרות שנראה שהם משתנים רגילים, אובייקטים של img מיושמים למעשה כמאגרים קטנים בין הפקודות. שימוש בתמונה כקלט לפונקציה "צורך" אותה והופך אותה לבלתי שימושית יותר. (מכאן הצורך בפקודות הכפולות)

מוּמלָץ:

בלוק הסכין האולטימטיבי: 11 שלבים (עם תמונות)

בלוק הסכין האולטימטיבי: כולנו היינו שם, קוצצים ירקות בעזרת סכין כל כך בוטה שיהיה יעיל יותר להשתמש בכפית. באותו רגע אתה מהרהר כיצד הגעת לשם: הסכינים שלך היו חדות כתער כשקנית אותם, אבל עכשיו, שלוש שנים בהמשך הדרך

ספקטרופוטומטר בלוק ג'נגה תוצרת בית לניסויי אצות: 15 שלבים

ספקטרופוטומטר גוש ג'נגה תוצרת בית לניסויי אצות: אצות הן פרוטאיסטים פוטוסינתטיים וככאלה הן אורגניזמים קריטיים בשרשראות מזון מימיות. אולם במהלך חודשי האביב והקיץ, מיקרואורגניזמים אלה ואחרים יכולים להתרבות ולהציף את משאבי המים הטבעיים, וכתוצאה מכך להידלדל חמצן

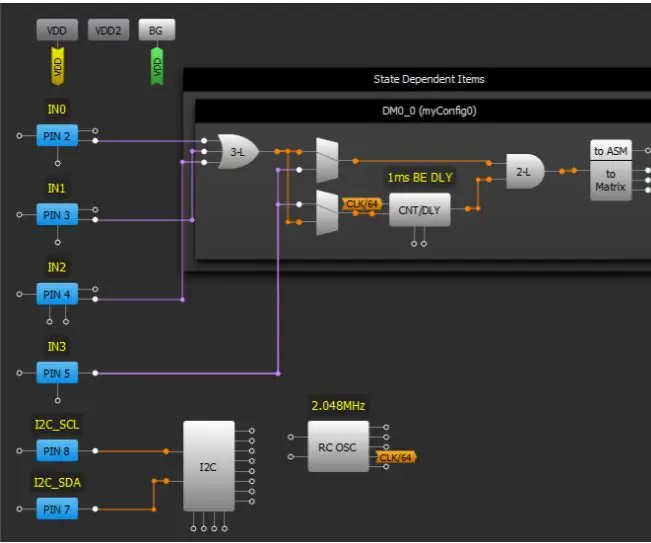

בלוק זיכרון דינמי DIY: 5 שלבים

בלוק זיכרון דינמי DIY: SLG46880 ו- SLG46881 מציגים מספר בלוקים חדשים שלא הופיעו במכשירי GreenPAK קודמים. הערת יישום זו מתארת את בלוקי הזיכרון הדינמי (DM) ואת אופן השימוש בהם. היתרון העיקרי של בלוקים DM הוא שניתן להגדירם מחדש

הזרמת וידיאו בשידור חי 4G/5G HD ממזל"ט DJI באיחור נמוך [3 שלבים]: 3 שלבים

![הזרמת וידיאו בשידור חי 4G/5G HD ממזל"ט DJI באיחור נמוך [3 שלבים]: 3 שלבים הזרמת וידיאו בשידור חי 4G/5G HD ממזל"ט DJI באיחור נמוך [3 שלבים]: 3 שלבים](https://i.howwhatproduce.com/images/009/image-25904-j.webp)

הזרמת וידאו בשידור חי 4G/5G HD ממזל"ט DJI באיחור נמוך [3 שלבים]: המדריך הבא יעזור לכם להשיג זרמי וידאו חיים באיכות HD כמעט מכל מזל"ט DJI. בעזרת אפליקציית FlytOS לנייד ויישום האינטרנט FlytNow, תוכל להתחיל להזרים וידאו מהמל"ט

שלט וידאו לפעוטות לנגן וידאו למחשב: 6 שלבים

שלט וידאו לפעוטות עבור נגן וידאו: אני בונה שלט רחוק שמתחבר למחשב עם USB. השלט הרחוק הגדול מאפשר לפעוט שלי לבחור ולהפעיל סרטונים במחשב ישן. זהו פרויקט פשוט יחסית. רכיב הליבה הוא לוח מקשים USB או לוח מקשים USB אלחוטי