תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:11.

- שונה לאחרונה 2025-01-23 14:46.

JDM הוא מתכנת PIC פופולרי מכיוון שהוא משתמש ביציאה טורית, מינימום של רכיבים ואינו דורש אספקת חשמל. אבל יש בלבול בחוץ, עם הרבה וריאציות מתכנתות ברשת, אילו מהן עובדות עם אילו PICs? ב"הנחיה "הזו אנו מעמידים את JDM במבחן ואני מדגים כיצד לדמות את המעגל באמצעות ספייס שיענה על כל השאלות שלך!

אספקה

LTspice אותו ניתן להוריד ממכשירי אנלוגי כאן.

אתה גם צריך את קבצי מעגל JDM כאן.

שלב 1: דרישות יציאה טורית

JDM דורש יציאה טורית העומדת במפרט EIA232, באופן אידיאלי עם +12/-12 רמות מתח.

על פי נתוני גיליון הנתונים MC1488 של Texas Instruments Line Driver (איור 3)

עכבת פלט = 4V/8mA = 500 אוהם.

מגבלת זרם קצר = 12mV, ללא הגבלת זמן - ללא נזק לשבב.

עכבת קלט של מקלט קו = 3k עד 7k ohm מומלץ.

יציאות סידריות במחשבים שולחניים ישנים יותר משתמשים +12v/-12V העונים על דרישה זו.

יציאות סידריות במחשבים ניידים חדשים משתמשים במתחים נמוכים יותר. JDM יכול לעבוד או לא - התשובה מורכבת יותר.

שלב 2: דרישות תכנות PIC

מידע בנוגע לדרישות התכנות של PIC מתקבל מ- Microchip. האמור לעיל מיועד למכשיר טיפוסי.

שלב 3: מפרט JDM

האם האתר המקורי של JDM הלך לאיבוד בערפילי הזמן? זה משאיר אותנו לנחש מה התכוון המעצב במקור למפרט.

- ספק VDD = 5V, ועד IDD = 2mA מרבי (לגרסת "in socket")

- ספק VHH = 13V, ועד IHH = 0.2mA מקסימום.

- זמן עלייה MCLR tVHHR = 1uS max.

- גרסת ICSP חייבת להיות מסוגלת למשוך את MCLR נמוך מול 22k משיכה למעלה למטרה.

שלב 4: תיאור המעגל

איור JDM1 מבוסס על מעגל ה- JDM "הסטנדרטי" שנלקח מאתר האינטרנט PICPgm. זהו מתכנת "PIC in Socket" שבו PIC לוקח כוח מסיכות TX ו- RTS. התרשים המקורי היה קשה להבנה ולכן ציירתי אותו מחדש באמצעות המוסכמה הרגילה של זרימת הזרם מלמעלה למטה. והוספתי מחווני LED "RESET", "PROG" ו- "RTS" הנחוצים במהלך הבנייה והבדיקות. אני מקווה שלאלו אין השפעה מזיקה על ההתנהגות.

האמנה הרגילה של עיצוב המעגלים היא המשותף לכל הסיבות, אך התכונה העיקרית של JDM היא שקרקע יציאה טורית (GND) מחוברת ל- VDD. זה יוצר בלבול כאשר אותות יציאה טורית נמדדים ביחס ל- GND, אותות PIC ביחס לקרקע לוגית (VSS).

כאשר TX עולה גבוה, Q1 מתנהג כשתי דיודות מוטות קדימה. (אספן Q1 אינו מוטה לאחור כמו בפעולת טרנזיסטור רגילה). אספן Q1 טוען C2, שהוא מהודק ב- VDD+8V על ידי זנר (D3). פולט Q1 מספק 13V ל- MCLR למצב תכנית/אימות.

כאשר TX יורד, הקבל C3 נטען דרך D1 ו- VSS נצמד ב- VDD-5V על ידי זנר (D5). TX גם מהודק ב (VSS-0.6) על ידי D1. Q1 כבוי, C1 מחזיק את החיוב שלו לדופק התכנות הבא. MCLR מהודק ב 0V על ידי D2, כך שה- PIC מתאפס כעת.

כאשר RTS גבוה, השעון מועבר ל- PGC. מהדק D4 PGC בהיגיון VDD גבוה. כאשר RTS נמוך, הקבל C3 נטען דרך D6 ו- VSS נצמד ב- VDD-5V על ידי זנר (D5). D6 מהדק PGC ב VSS או היגיון 0.

במהלך התכנות, הנתונים שנשלחים ב- DTR נקראים ב- PGD, אשר ה- PIC מגדיר כקלט. כאשר DTR גבוה, Q2 פועל כ"עוקב פולט "ומתח PGD הוא בערך (VDD-0.6) או היגיון 1. כאשר DTR נמוך, Q2 פועל כטרנזיסטור גרוע (פינים וסיכות אספן הפוכים). Q2 מושך את PGD נמוך, אשר מהודק על ידי D7 ב VSS או היגיון 0.

במהלך אימות ה- PIC מגדיר את PGD כפלט לשליחת נתונים ליציאה הטורית. יש להגדיר DTR גבוה, ולקרוא נתונים ב- CTS. כאשר פלט PGD גבוה, Q2 כבוי, CTS = DTR = +12V. כאשר פלט PGD נמוך, Q2 מופעל. אספן Q2 שואב זרם (12V+5V)/(1k+1k5) = 7mA מ- DTR, ומושך את CTS נמוך, ל- VSS.

שלב 5: היכונו לסימולציה

הורד תבלין LT, שמור ופתח את קבצי המעגלים (*.asc) המסופקים כאן. כדי לדמות את המעגל, עלינו לתת לו כמה כניסות, ולאחר מכן "לעקוב" אחר היציאות. V1, V2 V3 מדמים את היציאה הטורית של 12V עם עכבת הפלט R11, R12, R13.

- V1 מייצר 2 פעימות תכנית ב- TX מ- 0.5ms עד 4.5ms

- V2 מייצר פרץ של פולסי נתונים ב- DTR מ -1.5 עד 4.5ms

- V3 מייצר פרץ של פולסי שעון ב- RTS מ 0.5 עד 3.5 ms

הרכיבים V4, X1, R15 ו- R16 כולם חלק מהסימולציה.

- V4 מייצר 2 פולסים מ -2.5 עד 4.5ms לאימות נתונים.

- מגשר X1 מדמה OUTPUT ב- PGD.

- R15, R16 מדמים את "הטעינה" של PIC ב- VDD ו- MCLR.

שלב 6: שינויים עבור ICSP

איור JDM3 מציג את הגרסה לתכנות "במעגל". שינויים מהמקור הם

- החלף שקע ZIF במחבר ICSP.

- ה- PIC מופעל כעת על ידי אספקה למעגל היעד (V5).

- הסר זנר 5V (D5).

- הקבל הקטן של 100pF (C4) מועבר ליד ה- PIC במעגל המטרה.

- נוריות LED לוקחות חשמל מלוח המעגלים במידת האפשר.

- הנגד משיכה של MCLR (R10) והדיודה (D10) נדרשים במעגל המטרה.

- אַזהָרָה. לוח היעד חייב להיות בעל אספקה "צפה", באופן אידיאלי סוללה.

- אין לחבר את קרקע המטרה (VSS) למחשב/מחשב PC על ידי חיבור כל יציאות מחשב אחרות במקביל ל- JDM.

לאחר הדמיה של JDM1, הבעיה של זמן טעינה ארוך ב- C2 התבררה. לאחר קריאת פרוטנבואל נראה כי C2 ו- Q1 נוספו כשינוי למקור. אני לא יכול לחשוב מה C2 ו- Q1 נועדו לעשות מלבד ליצור בעיות. אז לגבי JDM4, נחזור לעיצוב הישן יותר של פרוטנבואל שהוא פשוט ופשוט להבנה. מהדק D1 ו- D3/LED2 MCLR בין VSS ל- VDD+8V. הערך של R1 מופחת ל -3 k3, מספיק רק כדי להאיר LED2 ב 12V.

JDM4 מיועד גם לעבודה עם יציאות טוריות חלשות יותר. כאשר TX עולה גבוה (+9V), מקור זרם TX = (9-8)/(1k +3k3) = 0.2ma, מספיק רק כדי למשוך MCLR גבוה אם כי אינו מספיק כדי להאיר LED2. כאשר TX יורד (בערך -7V), כיור זרם TX = (9-7)/1k = 2mA. זרם LED1 = (7-2 עבור לד)/(2k7) = 1.8mA. זרם MCLR למטה = 7-5.5/3k3 = 0.5mA.

מעגל זה נבדק גם הוא (סימולציית JDM5) כדי לראות מה קורה עם יציאות טוריות +/- 7V מינימום, כאשר אין מספיק מתח לקיים VHH = 13V. המטרה של C1 מתבררת כעת, C1 יוצר חיזוק קצר +ve ל- MCLR, זינוק של 33us בקצה העולה של TX, מספיק זמן מספיק כדי שה- PIC יכנס למצב תכנות, אולי? אבל הסר את מגשר X2 (השבת LED1) מכיוון שאין מספיק זרם כדי למשוך את MCLR נמוך ולהאיר את LED1 יחד. כאשר TX יורד, כיור זרם TX = (7V-5.5V)/(1k+3k3) = 0.3mA, מספיק רק כדי למשוך MCLR נמוך כנגד R10 הנפתח.

שלב 7: תוצאות סימולציה

כדי לצפות בקבצים הגרפיים, עדיף ללחוץ באמצעות לחצן העכבר הימני על הקישורים למטה, ולאחר מכן לבחור "פתח קישור בכרטיסייה חדשה"

סימולציה 1: עקבות של MCLR, VSS ו- RTS עבור JDM1 המקורי. תצפית 1, 2 ו -3 ניכרות מיד.

סימולציה 2: עקבות של MCLR ו- VSS ו- RTS עבור JDM2 שונה, המתקן בעיות קודמות.

סימולציה 3: עקבות של PGD, VSS ו- PGC לשליחת נתונים של JDM2 במצב תוכנית. תצפית 4 ב -3.5 mS.

סימולציה 4: עקבות של PGD, VSS ו- CTS עבור JDM2 במצב אימות (מגשר X1 מוכנס). בסדר

סימולציה 5: עקבות של MCLR, VSS, PGD ו- PGC עבור JDM3. שימוש ב- ICSP באמצעות כוח מהמעגל פותר בעיות רבות.

סימולציה 6: עקבות של MCLR, VSS, PGD ו- PGC עבור JDM4 עם יציאה טורית +/- 9V. MCLR עולה מיד, עובד באופן מלא.

סימולציה 7: עקבות של MCLR, VSS ו- TX עבור JDM5 עם יציאה טורית +/- 7V ומגשר X2 הוסר. C1 יוצר חיזוק +ve (קפיץ) בקצה העולה של MCLR, כמעט מספיק כדי לדחוף את MCLR מעל TX ל -13V.

שלב 8: מסקנות

ספייס ממש טוב לחשוף "סודות נסתרים" של פעולת מעגלים. מסתבר שמעגל JDM פועל ותואם לשבבי PIC רבים, אך התצפיות הבאות חושפות מגבלות/בעיות תאימות/תקלות אפשריות?

- זמן עלייה ארוך של MCLR בעוד C2 נטען ל- VPP על הדופק הראשון של TX. מפרט נכשל 3.

- היציאה הסדרתית טוענת C2 כאשר TX עולה גבוה ו- RTS יורד. אבל ל- RTS יש גם את התפקיד של טעינת C3. כאשר שניהם מתרחשים במקביל הדבר יוצר עומס רב יותר על RTS, וכתוצאה מכך C3 מאבד מטען (VSS עולה) ב -2 ms על סימולציה. מפרט נכשל 1.

- C3 מאבד את הטעינה (VSS מתחיל לעלות) לאחר שדופקי השעון עוצרים ב -3.5 ms.

- מה המטרה של C2, זה נחוץ בכלל?

פתרונות

- יש להניח ש- PICPgm משתמש בתוכנת "עבודה". הוא חייב להחיל דופק TX ארוך כדי לטעון מראש ל- C2, ואז להיכנס למצב תכנות רק לאחר הדופק השני של TX? לצורך הדמיה הפחתתי את הערך של C2 ל- 1uF כדי לתת זמן עלייה של 1ms. לא פתרון אידיאלי.

- פיצול C2 ו- C3 כך שהם נטעינים באופן עצמאי. שינוי קטן אחד ל- JDM2, C2 מופנה ל- GND במקום ל- VSS.

- נפתר על ידי JDM3. ICSP הרבה יותר אמין מכיוון ש- PIC מופעל על ידי מעגל מטרה.

- JDM4 פותר את הבעיה 1. זהו עיצוב פשוט שמבטל את C2 לגמרי.

שלב 9: ולבסוף

ההוכחה לפודינג היא באכילה. JDM זה עובד, המשך להשתמש בו.

וההמלצות שלי הן:

- השתמש ב- JDM2 לתכנות שקע ויציאות טוריות של 12V,

- השתמש ב- JDM4 עבור מתכנת ICSP ויציאות טוריות מעל +/- 9V,

- השתמש ב- JDM4 כאשר מגשר X2 מוסר ליציאות טוריות מעל +/- 7V.

הפניות:

תבלין אנלוגי LT תבלין

picpgm

פרוטנבואל

עקוב אחר פרויקטים נוספים של PIC בפינה ערמומית

מוּמלָץ:

סקירת Elegoo Super Started Uno R3: 4 שלבים

סקירת Elegoo Super Started Uno R3: לפני מספר ימים שלחה אלגו אליי את ערכת Super Starter זו לבדיקה. אז בואו נראה מה יש בפנים. בעת פתיחת המארז הקומפקטי הזה נוכל לראות הרבה דברים. על הכריכה יש אינדקס עם כל הרכיבים. בפנים יש לנו כרטיס תודה עם כל ה

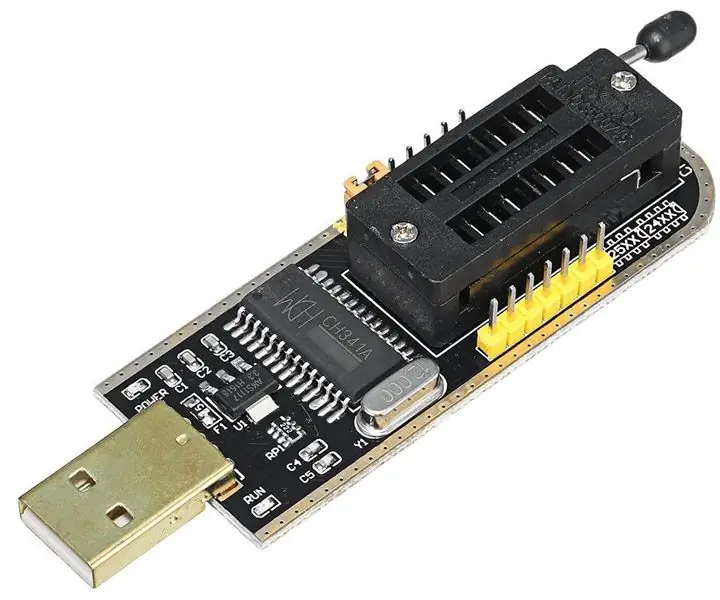

מתכנת CH341A: 8 שלבים

מתכנת CH341A: לאחרונה רכשתי מתכנת מיני CH341A. מתכנת המיני בסדר והוא יכול לתכנת שבבים מסדרה 24 ו -24. זה בעלות נמוכה מאוד אך שימושי למדי מכיוון שאני יכול להשתמש בו כדי להבהב את ה- BIOS של המחשב ואת הקושחה של הנתב

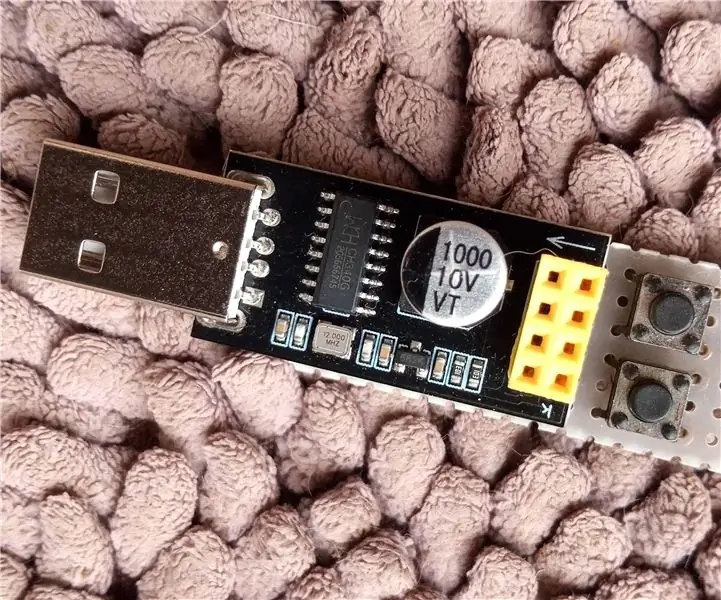

פריצת מתכנת ESP -01 - הפשוטה :): 6 שלבים

פריצת מתכנת ESP-01-הפשוטה :): היי ESPers, במדריך זה אראה לכם פריצה פשוטה לביצוע מתכנת עבור מודול ESP-01 / ESP8266-01 / ES-01. רובנו השתמשנו בלוח Arduino או התקני FTDI USB-TTL כמתכנתים עבור מודול זה. שתי השיטות עובדות מצוין. אבל לא

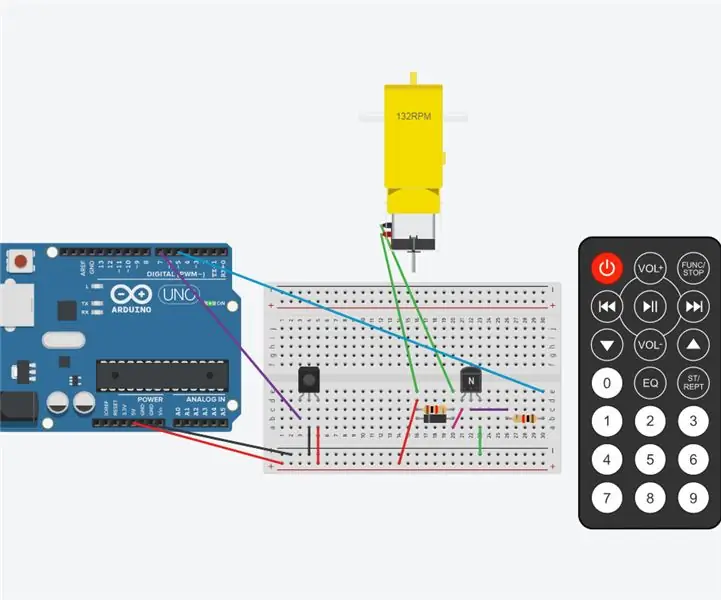

מנוע מבוקר טרנזיסטור עם שלט רחוק; סקירת מעגל: 9 שלבים

מנוע נשלט על ידי טרנזיסטור עם שלט רחוק; סקירת מעגל: מעגל זה הוא מנוע הנשלט על ידי טרנזיסטור עם שלט. השלט הרחוק מפעיל את ההפעלה. הטרנזיסטור יפעיל את המנוע. קוד התוכנית יגדיל את מהירות המנוע ו לאחר מכן הורד את מהירות המנוע עד לאפס

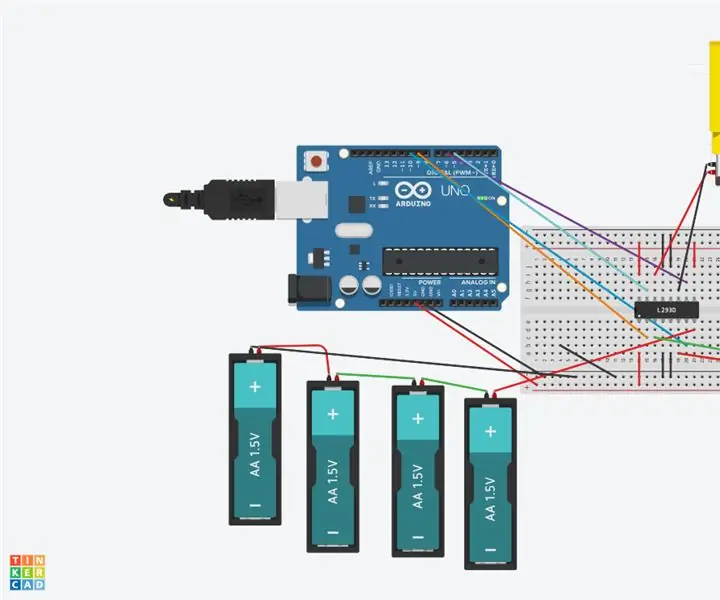

שימוש בגשר H (293D) להנעת 2 מנועי תחביבים מכוונים Ans Arduino; סקירת מעגל: 9 שלבים

שימוש בגשר H (293D) להנעת 2 מנועי תחביבים ממונעים Ans Arduino; סקירת מעגלים: גשר H 293D הוא מעגל משולב המסוגל להניע 2 מנועים. היתרון של גשר H על פני טרנזיסטורים או מעגלי בקרה MOSFET הוא שהוא יכול להניע את שני המנועים דו כיוונית (קדימה ואחורה) עם קוד