תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:14.

- שונה לאחרונה 2025-01-23 14:46.

אני המום מסוג התגובות שאני מקבל בבלוג הזה. תודה חבר'ה על הביקור בבלוג שלי והנעה אותי לשתף אתכם בידע שלי. הפעם, אני אציג את העיצוב של מודול מעניין נוסף שאנו רואים בכל ה- SOC - Interrupt Controller.

אנו נעצב בקר מפריע לתכנות פשוט אך רב עוצמה. זהו עיצוב הניתן להגדרה ולפרמטרים לחלוטין אשר נייד על פני פלטפורמות. תכננתי את זה לאחר שקראתי הרבה על כמה ארכיטקטורות פופולריות של בקר הפרעות, כמו NVIC, 8259a, RISC-V PLIC, Microblaze's INTC וכו '. בעזרת בקר הפרעות.

שלב 1: מפרטים

להלן המפרט של ה- IP:

- ממשק AHB3-Lite.

-

פרמטרים הניתנים להגדרה סטטית:

- מספר מקורות הפרעה חיצוניים; תומך בעד 63 הפרעות.

- מספר רמות עדיפות; תומך עד 63 רמות.

- מספר רמות הקינון; תומך עד 8 קינות ברמה.

- רוחב האוטובוס; 32 או 64.

- הפרעות גלובליות ומקומיות ניתנות להסרה.

- רמת עדיפות ניתנת להגדרה דינמית עבור כל הפרעה.

- שני מצבי פעולה - מצב מקונן לחלוטין ומצב עדיפות שווה.

- תומך בהפרעות רגישות ברמה פעילה-גבוהה.

בעיצוב נעשה שימוש במנגנון לחיצת יד בהפרעה של מפרטי RISC-V PLIC.

קדימה להפריע היא בהשראת 8259a

כתבות אחרות: Microblaze INTC, NVIC

שלב 2: סקירה כללית של PIC

בקר הניתנת לתכנות (PIC) מקבל הפרעות מרובות מציוד היקפי חיצוני וממזג אותן לפלט הפרעה יחיד לליבת מעבד מטרה.

PIC נשלט באמצעות רשימות בקרה ומעמד. כל רשימות ה- PIC ממופות בזיכרון, ונגישות אליהן באמצעות ממשק האוטובוס AHB3-Lite.

בנק הרשמים מורכב מרשם תצורות, מאגרי רישום, רישומים ממתינים, רגיסי שירות, רשימות עדיפות ורשום מזהים, האופייניים לבקרי הפרעות.

רשם התצורה משמש להגדרת אופן הפעולה של PIC. זה יכול לעבוד במצב מקונן לחלוטין או במצב עדיפות שווה.

לכל הפרעה ניתן להקצות סדרי עדיפויות ולמסוך אותם בנפרד. תמיכה גם במיסוך גלובלי של כל ההפרעות.

בנק הרשמים מתקשר עם Priority Resolver ו- BTC (Binary-Tree-Comparator) כדי לפתור את סדרי העדיפויות של הפרעות ממתינות ולקבוע את ההפרעה למעבד בהתאם. מרשם המזהים מכיל את המזהה של ההפרעה הממתינה בעדיפות הגבוהה ביותר.

שלב 3: עיצוב ויישום RTL

המתח העיצובי של PIC מצמצם את ההשהיה של פתרון עדיפויות, שהוא החלק הקריטי ביותר בעיצוב. מכיוון שהעיצוב פותר סדרי עדיפויות במחזור שעון אחד, הביצועים מתדרדרים עם הגידול במספר המקורות בעלי מורכבות Log2.

העיצוב יושם בהצלחה והתזמון אומת עד התדרים הבאים על FPGA של Artix-7.

- עד 15 מקורות: 100 מגה -הרץ

- עד 63 מקורות: 50 מגהרץ

איחור הפסק המתווסף על ידי PIC בלבד הוא 3 מחזורי שעון (לא כולל זמן מעבר ההקשר של המעבד וזמן האחזור הראשון של הוראות ISR).

שלב 4: הערות חשובות וקבצים מצורפים

הערות חשובות:

- אם ממשק AHB3-Lite אינו רצוי, תוכל לשנות את המודול העליון ולהשתמש בעיצוב השלד של PIC. אולם ספסל הבדיקה המסופק מיועד ל- IP עם ממשק AHB3-Lite.

- PIC IP v1.0 הוא עיצוב RTL נייד לחלוטין, חשוף.

- מאומת פונקציונלית לעבודה על שני המצבים.

קבצים מצורפים:

- עיצוב קודים ומשטח בדיקה ב- VHDL.

- תיעוד IP מלא.

זהו עיצוב קוד פתוח … אל תהסס להשתמש …

לכל שאלה, בכל עת:

מיטו ראג '

מוּמלָץ:

555 טיימר לפליט אות להפסקת Atmega328: 7 שלבים

555 טיימר לפליט אות להפסקת Atmega328: המטרה העיקרית של מעגל זה היא חיסכון באנרגיה. לכן, אני לא הולך לדבר על ארדואינו כי ללוח עצמו יש תקרת כוח מיותרת עבור מוצר סופי. זה נהדר לפיתוח. אבל, לא טוב במיוחד לפרויקטים אחרונים הפועלים על באט

בקר - בקר Vivarium: 6 שלבים

Freya - בקר Vivarium: Freya הוא קוד בקרה, מערכת בקרת vivarium מבוססת Raspberry Pi. במדריך זה אנו הולכים לעבור את השלבים של הכנת הבקר

בקר משחק DIY מבוסס Arduino - בקר משחקים Arduino PS2 - משחק Tekken עם לוח המשחקים Arduino DIY: 7 שלבים

בקר משחק DIY מבוסס Arduino | בקר משחקים Arduino PS2 | משחק Tekken עם DIY Arduino Gamepad: שלום חבר'ה, משחקים זה תמיד כיף, אבל משחק עם בקר DIY מותאם אישית משלך הוא יותר כיף. אז נכין בקר משחק באמצעות arduino pro micro במדריך זה

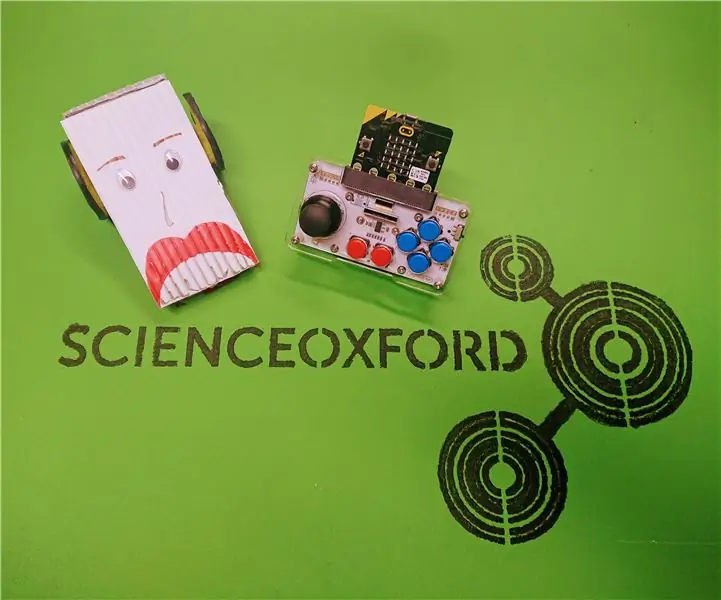

תכנות מיקרו: רובוט ביט וג'ויסטיק: בקר סיביות עם מיקרופייתון: 11 שלבים

תכנות Micro: Bit Robot & Joystick: בקר Bit עם MicroPython: עבור Robocamp 2019, מחנה הרובוטיקה הקיץ שלנו, צעירים בגילאי 10-13 הלחמים, מתכנתים ובונים מיקרו: רובוט מבוסס ביט, מבוסס ביט, כמו גם תכנות מיקרו: ביט לשימוש כשלט רחוק. אם אתה נמצא כעת ברובוקמפ, סקי

עיצוב לוח פיתוח מיקרו -בקר: 14 שלבים (עם תמונות)

תכנון לוח פיתוח מיקרו -בקר: האם אתה יוצר, חובב או האקר המעוניין להתגבר מפרויקטים של פרפבורד, מכשירי DIP ומחשבי PCB תוצרת בית למחשבי PCB מרובי שכבות המיוצרים על ידי בתי לוח ואריזות SMD מוכנות לייצור המוני? אז ההנחיה הזו היא בשבילך! הגוי הזה