תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:14.

- שונה לאחרונה 2025-01-23 14:46.

במדריך זה אנו הולכים לעצב בקר VGA פשוט ב- RTL. בקר VGA הוא המעגל הדיגיטלי שנועד להניע מסכי VGA. הוא נקרא מתוך מאגר מסגרות (זיכרון VGA) המייצג את המסגרת להצגה, ומייצר נתונים וסינכרים נחוצים לצורך תצוגה.

אם אתה מחפש קוד Verilog/verilog מערכת: בקר בקר שלי בבלוג VGA ובמערכת וידאו ב- Verilog

שלב 1: ממשק של בקר VGA

להלן אותות הממשק העיקריים בבקר VGA

- שעון פיקסל או שעון VGA

- אותות HSYNC ו- VSYNC

עבור תצוגת VGA שנבחרה, תחילה עליך לחשב את התדירות של שעון פיקסל הדרוש להנעתו. זה תלוי ב -3 פרמטרים: סה"כ פיקסלים אופקיים, סה"כ פיקסלים אנכיים, קצב רענון המסך.

בדרך כלל, F = THP * TVP * קצב רענון

מצא את התיעוד לגבי שעון הפיקסלים הדרוש למסכי VGA שונים, ב- RAR המצורף.

אותות HSYNC ו- VSYNC נוצרים משעון פיקסל. העיתוי של אותות HSYNC ו- VSYNC תלוי במספר הפרמטרים: חזית אופקית ואנכית, חזית אחורית אופקית ואנכית, פיקסלי תצוגה אופקיים ואנכיים, רוחבי דופק אופקי ואנכי ואנכי.

פרמטרים אלה מתוקננים לתצוגת VGA שנבחרה. מצא מסמכים אלה ב- RAR המצורף.

פרמטרים אלה הם פרמטרים הניתנים להגדרה ב- VGA בקר ה- VGA שלנו.

שלב 2: שילוב של בקר VGA עם צג VGA

האיור מראה כיצד ניתן לשלב בקר VGA עם צג VGA. אתה צריך שני רכיבים נוספים להשלמת המערכת:

- מאגר מסגרות: זיכרון שמחזיק את המסגרת להצגה.

- DAC וידאו: DAC הממיר נתונים דיגיטליים של RGB ומניע את תצוגת VGA עם אותות אנלוגיים RGB ברמת מתח מתאימה.

אחד מחשבי ה- DAC הפשוטים והפופולריים של וידאו הוא ADV7125. זהו DAC של 8 סיביות הממיר מילים דיגיטליות של RGB לאותות אנלוגיים של 0-0.7 V ומניע את תצוגת VGA.

שלב 3: עיצוב מאגר מסגרות

הזיכרון הוא זה שאוחסן את התמונה המוצגת. זה בדרך כלל זיכרון RAM או לפעמים ROM. נדון כיצד לעצב מאגר מסגרות לייצוג תמונה. מאגר מסגרות מעביר את המידע הדיגיטלי הזה לפקודת DAC בווידיאו מבקר VGA.

ראשית עלינו להחליט על עומק הפיקסלים הדרוש. היא קובעת את איכות התמונה, את מגוון הצבעים שפיקסל יכול לייצג. עבור DAC של 8 סיביות, עלינו לייצג את מרכיבי הצבע העיקריים של פיקסל: R, G ו- B ב -8 סיביות כל אחד. זה אומר, פיקסל הוא של 24 סיביות.

כל פיקסל מאוחסן באופן רציף במיקומי זיכרון Frame Buffer.

נניח שהתמונה שתוצג תהיה בגודל 800x600 פיקסלים.

לכן הצורך במאגר מסגרת הוא 800x600 = 480000 x 24 סיביות זיכרון

גודל הזיכרון הכולל הוא 800x600x24 = 1400 kB בערך.

אם תמונה בשחור -לבן, 800x600x1 = 60 kB בערך.

זיכרונות בלוק עשויים לשמש לייצוג מאגר מסגרות ב- FPGA של Xilinx.

שלב 4: הערות

- יש צורך באותות נוספים בבקר VGA בהתאם ל- DAC שנבחר. השתמשתי ב- ADV7125.

- הוסף עיכובים במחזור באמצעות כפכפים ב- VSYNC ו- HSYNC לפני שאתה נוסע בתצוגת VGA. הסיבה לכך היא DAC וזמני השהיה. יש לסנכרן את אותות הפיקסל עם HSYNC ו- VSYNC. במקרה שלי, זה היה עיכוב של 2 מחזורים.

- אם לא ניתן לעצב את מאגר מסגרות בגודל נתון ב- FPGA עקב מגבלת גודל חסימת RAM, השתמש בזיכרון קטן יותר לייצג את התמונה ופשוט ערוך את הקוד כדי לגלגל את הכתובת בגבול הזיכרון הזמין, ולא בגבול המסגרת המלאה. זה ישכפל את אותה התמונה שוב ושוב לאורך כל המסך. שיטה נוספת היא קנה מידה של פיקסל שבו כל פיקסל משוכפל כדי להציג את התמונה כולה במסך מלא, ברזולוציה פחותה. זה יכול להיעשות על ידי התאמת לוגיקת הגדלת כתובות בקוד.

- ה- IP נייד לחלוטין בכל FPGAs ומאומת תזמון עד 100 מגה-הרץ ב- Virtex-4 FPGA.

שלב 5: קבצים מצורפים

ה- RAR מכיל:

- קוד בקר VGA

- מסמכי PDF של תקני VGA.

מוּמלָץ:

שעון ניקסי עם ארדואינו - עיצוב פשוט ביותר: 4 שלבים

שעון ניקסי עם ארדואינו | עיצוב פשוט ביותר: לאחר יום עבודה ארוך, סוף סוף הצלחתי לייצר שעון ניקסי עם ארדואינו ושבב בידוד אופטי, אין צורך בדרייבר של ניקסי שקשה לרכוש אותו

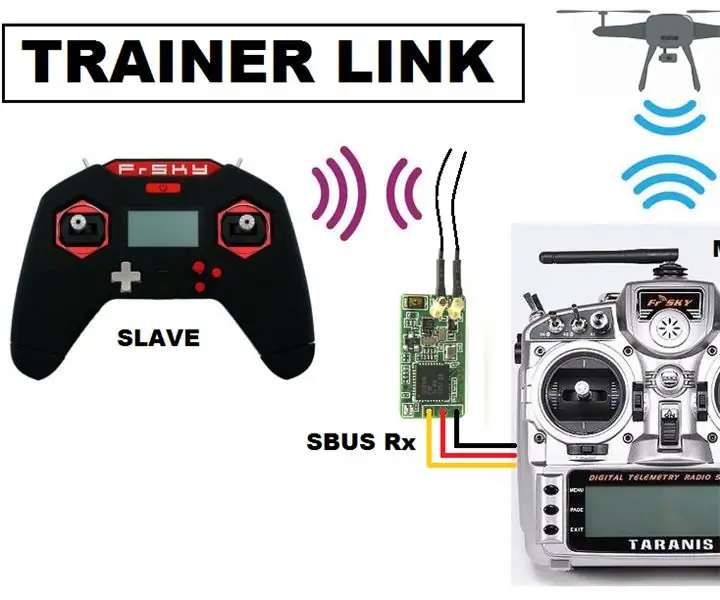

מאמן Taranis X9D+ פשוט פשוט באמצעות קלט מקלט SBUS: 9 שלבים

פשוט Taranis X9D+ מאמן אלחוטי באמצעות קלט מקלט SBUS: מטרת הפרויקט היא לחבר משדר FrSky X-Lite למשדר FrSky X9D+ בתצורת TRAINER באמצעות מקלט SBUS זול (12 $). על ידי חיבור השניים בצורה זו, אפשר לטייס מדריך באמצעות

עיצוב לוח פיתוח מיקרו -בקר: 14 שלבים (עם תמונות)

תכנון לוח פיתוח מיקרו -בקר: האם אתה יוצר, חובב או האקר המעוניין להתגבר מפרויקטים של פרפבורד, מכשירי DIP ומחשבי PCB תוצרת בית למחשבי PCB מרובי שכבות המיוצרים על ידי בתי לוח ואריזות SMD מוכנות לייצור המוני? אז ההנחיה הזו היא בשבילך! הגוי הזה

כיצד להרכיב בקר ידית פשוט ועוצמתי- מבוסס על המיקרו: ביט: 10 שלבים (עם תמונות)

כיצד להרכיב בקר ידית פשוט ועוצמתי- מבוסס על המיקרו: ביט: שם הידית הוא Handlebit. הצורה היא ידית והיא נראית מגניבה מאוד! עכשיו נוכל לערוך הקדמה אודות ה- Handlebit, בואו נעבור עליה

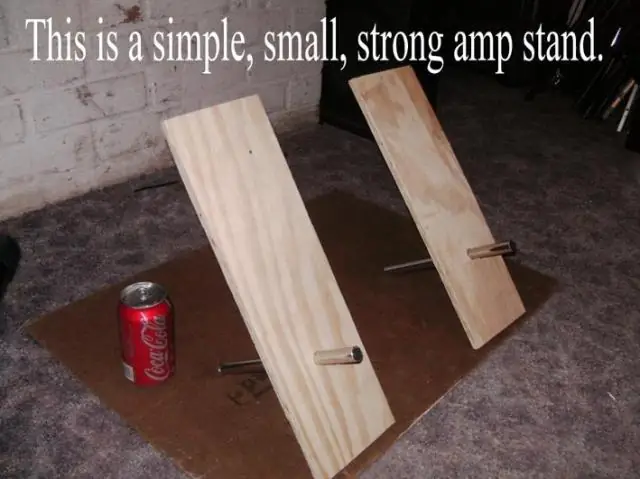

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: 9 שלבים

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: מעמד הטיה למגבר גיטרה - קל מדי - פשוט, קטן, חזק, חינם או ממש זול. לכל אמפר בכל גודל, אפילו ארונות גדולים עם ראש נפרד. פשוט צור לוחות וצינורות בגודל ואתה צריך כמעט לכל ציוד שאתה רוצה