תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:17.

- שונה לאחרונה 2025-01-23 14:46.

זהו הדרכה כיצד לבנות שעון עצר של דקה אחת באמצעות VHDL ולוח Basys 3. מכשיר כזה הוא אידיאלי למשחקים שבהם לכל שחקן יש מקסימום דקה אחת לבצע את המהלך שלו. שעון העצר מציג במדויק שניות ואלפיות השנייה בתצוגת שבעה הפלחים, החל מ -0 שניות ו -0 מילי -שניות, עד 60 שניות ו -0 מילי -שניות. שני כפתורים משמשים גם: הכפתור המרכזי, המשמש להפעלה, עצירה והמשך הטיימר, והכפתור הימני, המשמש להפעלה מחדש של הטיימר. כאשר המכשיר מושווה זה לצד זה עם שעון העצר המובנה של טלפון חכם, דיוק השעון מורגש.

שלב 1: השגת חומרה/תוכנה

1. לוח Basiner 3 Artix-7 FPGA מאמן Digilent עם כבל מיקרו USB ל- USB

2. Vivado 2016.2 סוויטת עיצוב מבית Xilinx

שלב 2: חסום תרשים

מעגל זה בנוי בהתנהגות ומשתמש ברכיבי Xilinx מובנים, אך ניתן לתאר אותו גם מבחינה מבנית, כפי שמוצג בתרשים המבני הכללי לעיל. מהתרשים ניתן לראות כי המעגל מונע על ידי שני מחיצות תדרים. אחד ממחלקי התדרים פועל במהירות של 1 סנטיש שנייה ומניע את מונה הקתודה המשמש כמספרים המוצגים בתצוגה של שבעה קטעים. מחלק התדרים השני פועל במהירות 240 הרץ ומשמש להנעת מונה האנודה המסתובב בין האנודות כך שכל המספרים יוצגו כראוי בתצוגת שבעה המגזרים. המקודד לוקח את ההיגיון הקתודה מונה הקתודה ואת ההיגיון של האנודה ממונה האנודה, ומקודד אותו לקתודה של היציאה ולאנודה שמפעילים את התצוגה של שבעה פלחים. תפקידו של מקודד זה הוא שיציאת הקתודה משתנה בכל פעם שפלט האנודה משתנה. לא ניתן להריץ את פלט הקתודה באופן עצמאי מן המונה מכיוון שהאנודות חייבות להסתובב דרך 4 הספרות הנפרדות.

שלב 3: מודול הפרויקט

ראשית, חסימת תהליך עבור CEN מתבצעת כך שכאשר תתגלה לחיצה על לחצן, ה- ENABLE יתחלף. זה משמש כתחנה/התחלה של מונה הקתודה.

בגוש התהליכים הבא, אותות השעון של סנטיש שנייה ו -240 הרץ מוגדרים כך שהמונים שלהם יגדלו ב -1 בכל פעם שהשעון הפנימי של 100 מגהרץ יגיע לקצה עולה. ברגע שמונה הסנטי שניות יגיע ל 500000, הוא יתאפס בחזרה ל 0. בינתיים מונה 240 הרץ יתאפס ברגע שהספירה תגיע ל 41667.

עבור קטע הקתודה בקוד, אם ENABLE הוא '0' ספירת הקתודה תשהה. אם לוחצים על כפתור האיפוס במהלך הזמן הזה, כל הספירות מתאפסות ל "0000". בינתיים, אם ENABLE הוא '1', ספירת הקתודות תימשך עד שמספר הקתודות יגיע ל -60.00, שבו הוא מפעיל את אות העצירה להיות '1'. אות העצירה מפנה חזרה לבלוק תהליך CEN וגורם ל- ENABLE להיות '0' בזמן שאות העצירה הוא '1' ולא ישתנה עד ללחיצת כפתור האיפוס.

לבסוף, תצוגת שבעה הקטעים מוגדרת על ידי כך שארבעת האנודות מחוברות כהלכה עם כל אחת משמונה הקתודות שלהן כדי להציג את הספרות המתאימות שלהן 0-9 בו זמנית.

שלב 4: אילוצים

קובץ אילוצים זה מחבר את הכניסות והיציאות שצוין מ- VHDL לחלקים הפיזיים ההכרחיים של לוח Basys. לפרויקט זה, הרכיבים כוללים את ארבעת האנודות וכל אחת משמונה הקתודות שלהן לתצוגת שבעה הקטע, השעון הפנימי של 100 מגה -הרץ, הכפתור המרכזי והכפתור הימני.

שלב 5: בדוק

לאחר השלמת הקוד, כעת תוכל לתכנת את ה- FPGA באמצעות כבל ה- USB. תצוגת שבעת הקטע צריכה להציג 0.00. בדוק אם הלחצנים פועלים על ידי לחיצה על הכפתור המרכזי כדי להפעיל את הטיימר עד שיגיע ל -60.00 ויעצור; בכל זמן שביניהם, תוכל ללחוץ שוב על הכפתור המרכזי כדי להשהות אותו. ברגע שהוא מושהה, תוכל ללחוץ על הכפתור הימני כדי לאפס את הטיימר בחזרה ל -0.00. אם הכל עובד כמו שצריך, כל הכבוד שבנית הרגע טיימר של דקה אחת!

מוּמלָץ:

סובב שעון חול בכל דקה באמצעות מנוע סרוו - ארדואינו: 8 שלבים

סובב שעון חול בכל דקה באמצעות מנוע סרוו - ארדואינו: במדריך זה נלמד כיצד לסובב שעון חול קטן (דקה אחת) כל 60s באמצעות מנוע סרוו ו- Visuino, צפה בסרטון הדגמה

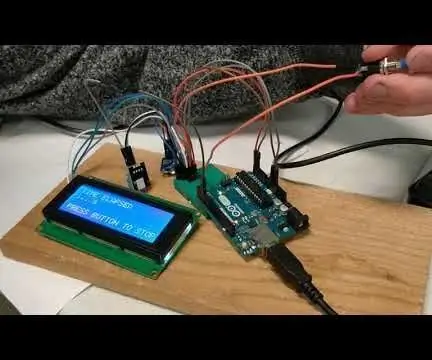

שעון עצר ארדואינו לאונרדו: 3 שלבים

שעון עצר ארדואינו לאונרדו: אשראי: https://www.instructables.com/id/Arduino-Stopwatch… עיצוב שעון העצר הזה מקורו בקישור שלמעלה, שהוא שעון עצר הסופר מ -1, ואילו זה סופר לאחור מ -60 שניות . רוב הקוד שהשתמשתי עוקב אחר המקור

שעון עצר בסיסי באמצעות לוח VHDL ו- Basys3: 9 שלבים

שעון עצר בסיסי באמצעות לוח VHDL ו- Basys3: ברוכים הבאים למדריך כיצד לבנות שעון עצר באמצעות לוח VHDL בסיסי ו- Basys 3. אנו שמחים לשתף אתכם בפרויקט שלנו! זה היה פרויקט גמר לקורס CPE 133 (עיצוב דיגיטלי) ב- Cal Poly, SLO בסתיו 2016. הפרויקט שהקמנו

שעון Arduino פשוט / שעון עצר: 6 שלבים (עם תמונות)

שעון / סטופר ארדואינו פשוט: " להנחיה זו " יראה וילמד אותך כיצד להכין שעון Arduino Uno פשוט המשמש גם כשעון עצר בכמה צעדים פשוטים

שעון עצר VHDL: 8 שלבים (עם תמונות)

שעון עצר VHDL: זהו הדרכה כיצד להכין שעון עצר באמצעות VHDL ולוח מעגלים מסוג FPGA, כמו לוח Basys3 Atrix-7. שעון העצר מסוגל לספור בין 00.00 שניות ל -99.99 שניות. הוא משתמש בשני כפתורים, אחד ללחצן התחלה/עצירה ואחד אחר