תוכן עניינים:

- שלב 1: חסום תרשים

- שלב 2: עקרון הפעולה

- שלב 3: יישום לוגי

- שלב 4: פתרון מבוי סתום

- שלב 5: תצורת התקנים - מעגל Matrix0

- שלב 6: תצורת התקנים - לוגיקת שעון SPI

- שלב 7: תצורת התקנים - מאפייני רכיבי Matrix0

- שלב 8: תצורת התקנים - מעגל Matrix1

- שלב 9: תצורת התקנים - מונה בינארי 3 סיביות

- שלב 10: תצורת התקנים - היגיון השוואת 3 סיביות

- שלב 11: תצורת מכשירים - היגיון השוואות דיגיטליות ורישום זמני

- שלב 12: תצורת התקנים - מאפייני רכיבי Matrix1

- שלב 13: תוצאות

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:13.

- שונה לאחרונה 2025-01-23 14:46.

מערכות בקרה והתקנים נלווים עוסקים במקורות חשמל מרובים, כגון קווי הטיה או סוללות, ועליהם לעקוב אחר הקו הגבוה ביותר (או הנמוך ביותר) בין קבוצה נתונה.

לדוגמה, החלפת עומס במערכת "מרובת סוללות" מחייבת שהמערכת תעקוב אחר המתח המינימלי או המרבי בין מערך הסוללות (מקסימום או דקה כפונקציה של אלגוריתם המיתוג המסוים) ותנתב את העומס באופן דינמי אל המקור המתאים ביותר בזמן אמת. לחלופין, המערכת עשויה להזדקק לביטול זמני של חיבור הסוללה במתח הנמוך ביותר לטעינה תקינה.

דוגמה נוספת היא מערכת החשמל הסולארית המודרנית, שבה כל פאנל סולארי מצויד במנגנון tiltrotate ובמעגל מעקב סולארי (האחרון מספק מידע על מיקום השמש לכיוון הפנל). בעזרת המידע על המתח המרבי, ניתן לכוונן כל מיקום של פאנל סולארי על בסיס לוח המחרוזת המספק למעשה את מתח המוצא הגבוה ביותר, ובכך להשיג רמה מעולה של אופטימיזציה של הספק.

ישנם מספר מותגים שונים של IC מסחריים (בעיקר מיקרו -בקרים) שיכולים באופן עקרוני ליישם עוקב מתח מרבי. עם זאת, הם דורשים תכנות והם פחות חסכוניים מאשר פתרון מעורב אותות. השלמת עיצוב Dialog GreenPAK ™ יכולה להשפיע לטובה על המחיר, הגודל והמודולריות של העיצוב. עיצוב זה מנצל את היתרון של שילוב מעגלים אנלוגיים ודיגיטליים בשבב אחד.

במדריך זה מיושם החזית האנלוגית וההיגיון הדיגיטלי הנדרש ליישום מאתר מתח מקסימלי (או בסופו של דבר דק) בין שמונה מקורות מובחנים.

כדי ליישם את צג המתח האנלוגי המרבי/דקה של 8 ערוצים, משתמשים ב- SLG46620G.

להלן תיארנו את הצעדים הדרושים להבין כיצד הפתרון תוכנת ליצירת צג מתח מקסימום/דקה אנלוגי בן 8 ערוצים. עם זאת, אם אתה רק רוצה לקבל את התוצאה של התכנות, הורד את תוכנת GreenPAK כדי לצפות בקובץ העיצוב GreenPAK שכבר הושלם. חבר את ערכת הפיתוח של GreenPAK למחשב שלך והקש על התוכנית ליצירת צג מתח מקסימום/דקה אנלוגי בעל 8 ערוצים.

שלב 1: חסום תרשים

איור 1 מציג את התרשים הגלובלי של המערכת המיושמת.

מחרוזת של עד 8 מקורות מתח משתנים מרובעת וממשקת למודול ADC של GreenPAK המחובר לעיצוב פנימי מותאם המסוגל לבחור את המקור בעל המתח הגבוה ביותר ביחס לאחרים. ההיגיון הפנימי מוציא מידע זה להצגה או לעיבוד נוסף.

העיצוב מבוסס על המוצר GreenPAK SLG46620G, מכיוון שהוא מכלול את כל אבני הבניין האנלוגיות והדיגיטליות הדרושות ליישום. ביישום זה המערך נסרק באמצעות מרבב אנלוגי ADG508 המונע ישירות על ידי ה- GreenPAK IC.

מידע הפלט הוא מספר דיגיטלי של 3 סיביות המתאים למספר המתח במתח מרבי. דרך ישירה לקבל מידע זה היא הצגת המספר באמצעות תצוגה של 7 קטע. ניתן להשיג זאת בקלות על ידי ממשק הפלט הדיגיטלי של SLG46620G למנהל התצוגה של 7 פלחים, כגון פתרון GreenPAK המתואר ב Reference או ל- IC 74LS47 נפוץ.

המעגל המוצג מחפש מתח מרבי. כדי להמיר את העיצוב לממצא מתח מינימלי, יש להוסיף מעגל פשוט לפני התניה בין המרבב האנלוגי לבין הכניסה האנלוגית GreenPAK, תוך חיסור יציאת המרבב ממתח התייחסות של 1 וולט.

שלב 2: עקרון הפעולה

התכנון נועד לבחור את המקור עם מתח מרבי, ולכן מתבצעת סריקה על כל המערך תוך אחסון הערך-מקסימום האחרון והשוואתו עם הערך הבא בכניסה (השייך למקור המתח הבא בסריקה).

בהמשך נתייחס לרצף ריבוב מלא שלם לאורך כל הכניסות כ"סריקה "או" לולאה ".

השוואה בין שני ערכים לא מתבצעת באמצעות רכיבי ACMP (עם זאת, זמין ב- SLG46620G), אלא על ידי מודול DCMP, ברגע שהערכים מתועברים דיגיטציה בהתאמה. זוהי טכניקה מתקדמת ומעודנת שבה נדון לראשונה ב- Reference.

איור 2 מראה כיצד בנוי SLG46620G לעיצוב זה.

אות הכניסה האנלוגי עובר לכניסת ADC דרך רכיב ה- PGA עם רווח מוגדר של 1. הגדרות רווח שונות אפשריות גם כדי למצוא את ההתאמה הטובה ביותר עם אלקטרוניקה מיזוג קדמית המוקדשת למיפוי מתח הכניסה ל- 0-1 V טווח המודול של GreenPAK ADC.

ה- ADC פועל במצב חד-צדדי וממיר את האות האנלוגי לקוד דיגיטלי של 8 סיביות, המועבר לאחר מכן למודול DCMP. הקוד הדיגיטלי מוזר גם לתוך בלוק SPI, המוגדר כמאגר ADC/FSM, שבו ניתן לאחסן קוד דיגיטלי ולא ישתנה עד שהדופק הבא יגיע לכניסת SPI CLK. שים לב שחסימת לוגיקה ייעודית מניעה את קלט SPI CLK. נחקור חלק זה מאוחר יותר, מכיוון שזהו ההיגיון "הליבה" האחראי לפעולה תקינה. קוד דיגיטלי חדש נשמר במודול SPI רק אם הוא שייך למתח הכניסה המרבי בפועל.

רכיב DCMP משמש להשוואת נתוני ADC הנוכחיים עם הזוכה האחרון (כלומר המקסימום האחרון שנמצא) המאוחסן בבלוק SPI. הוא יפיק דופק ביציאת OUT+ כאשר נתוני ADC חדשים גדולים מהקודם. אנו משתמשים באות OUT+ כדי לעדכן את בלוק SPI עם הזוכה החדש.

אות שעון גלובלי מניע המרות ADC ותזמונים כלליים. לאחר ביצוע המרה, אות הפלט INT של ה- ADC פועם, המתואם בזמן עם פלט הנתונים המקביל של ADC. אנו משתמשים בפלט INT גם כדי להגדיל מונה בינארי של 3 סיביות, המיושם על ידי DFFs ב- Matrix1, וזה שימושי משלוש סיבות:

1. קווי הפלט המונה פונים למכפיל האנלוגי החיצוני, ובכך משרתים את מתח הכניסה הבא ל- ADC;

2. הספירה מוקפאת לרשם 3 סיביות (מיושם במטריקס 1) לאחסון הזוכה הזמני במהלך סריקה;

3. הספירה מפוענחת לעדכון רישום 3 סיביות שני (המיושם ב- Matrix0) לאחר השלמת הסריקה.

שלב 3: יישום לוגי

מודול ה- ADC מספק ברצף נתונים המומרים של כל מתח הכניסה, אחד אחרי השני, ללא הגבלת זמן. לאחר שמכפילים את המרבב 0b111 (עשרוני 7), המונה מתגלגל ל -0b000 (0 עשרוני) ובכך מתחיל סריקה חדשה של מתח הכניסה.

במהלך הסריקה, אות הפלט ADC INT נוצר כאשר פלט הנתונים המקביל הוא תקף. כאשר אות זה פועם, המכפיל האנלוגי חייב לעבור לכניסה הבאה, ומספק ל- PGA את המתח המתאים. לכן, פלט ADC INT הוא אות השעון הישיר של המונה הבינארי 3 סיביות באיור 2, שמילת הפלט המקבילית שלו 3 סיביות פונה ישירות למכפיל האנלוגי החיצוני ("V בחר" באיור 1).

נתייחס כעת לדוגמא שבה מתח הכניסה אמור להיות בעל הקשרים הבאים:

א) V0 <V1 <V2

ב) V2> V3, V4

ג) V5> V2

איור 3 מייצג את האותות העיקריים המעורבים במנגנון ההחלטה המרבי.

מכיוון שבסופו של דבר הנתונים מתעדכנים לתוך מאגר SPI באופן סינכרוני עם פולסי INT, קיים חלון השוואה שבו תוכן מאגר SPI מושווה לתוצאת ההמרה הבאה של ADC. תזמון מסוים מביא ליצירת פולסים OUT+ ביציאת DCMP. אנו יכולים לנצל את הפולסים הללו כדי לטעון ערכים חדשים לרשם מאגר SPI.

כפי שעולה משורת הנתונים של מאגר SPI באיור הקודם, פנקס ה- SPI תמיד מכיל, פעם אחר פעם, את הערך הגדול ביותר מבין 8 הכניסות והוא מתעדכן רק כאשר מזהה ערך גדול יותר על ידי מודול DCMP (הכוונה ל- DCMP OUT+ קו המוצא של העלילה, הפולסים החסרים גורמים ל- V2 להישאר נעולים במרשם עד להשוואה עם V5).

שלב 4: פתרון מבוי סתום

אם ההיגיון המיושם יהיה בדיוק כפי שתואר לעיל, ברור שאנו נתקלים במצב של מבוי סתום: המערכת מסוגלת לזהות רק מתח גבוה מזה המתאים למה שאוחסן ברשם החיץ SPI.

זה תקף גם במקרה שהמתח הזה ירד ואז קלט אחר, עד עכשיו נמוך מזה, יהפוך לגבוה ביותר: הוא לעולם לא יתגלה. מצב זה מוסבר טוב יותר באיור 4 בו קיימים רק 3 מתח כניסה למען בְּהִירוּת.

בזמן איטרציה 2, V3 יורד ו- V1 הוא המתח המקסימלי בפועל. אבל מודול ה- DCMP אינו מספק דופק מכיוון שהנתונים המאוחסנים ברשם החיץ SPI (המקביל ל -0.6 V) גדולים מזה המקביל ל- V1 (0.4 V).

לאחר מכן המערכת מתנהגת כמציאת מקסימום "מוחלטת" ואינה מעדכנת את הפלט בצורה נכונה.

דרך טובה להתגבר על בעיה זו היא לאלץ את טעינת הנתונים מחדש לרשומת מאגר SPI כאשר המערכת תסיים מחזור סקר מלא של כל הערוצים.

למעשה, אם המתח בכניסה זו עדיין הגבוה ביותר, שום דבר לא משתנה והבקרה ממשיכה בבטחה (בהתייחס לאיור 4 לעיל, זהו המקרה של איטרציות לולאה 0 ו -1). מצד שני, אם המתח בכניסה זו במקרה יורד לערך פחות מאשר קלט אחר, טעינת הערך מחדש מאפשרת למודול DCMP לייצר דופק OUT+ כאשר משווים אותו לערך המקסימלי החדש (זהו במקרה של Loop Iterations 2 ו- 3).

יש צורך במעגל לוגי כדי להתגבר על הבעיה. הוא חייב ליצור אות שעון לרכיב ה- SPI כאשר הלולאה מגיעה לקלט המרבי בפועל, ובכך לאלץ טעינה מחדש של מילת הנתונים המעודכנת שלה לרשם מאגר SPI. זה יידון בסעיפים 7.2 ו -7.6 להלן.

שלב 5: תצורת התקנים - מעגל Matrix0

ל- SLG46620G שני בלוקים מטריקס, כפי שמתואר באיור 2. האיורים הבאים מראים את תצורות ההתקן המתאימות.

החלק העליון של המעגל הוא "רישום הלולאה" שממומש עם 3 DFFs (DFF0, DFF1 ו- DFF2). הוא מתרענן לאחר כל לולאה של מכפיל הקלט כדי לשלוח למנהל התצוגה של 7 פלחים את המספר הבינארי של "הזוכה", כלומר הקלט בעל המתח הגבוה ביותר בסריקה האחרונה. הן השעון ל- DFFs והן הנתונים מגיעים מההיגיון המיושם ב- Matrix1 דרך, בהתאמה, יציאה P12, P13, P14 ו- P15.

החלק התחתון הוא החזית האנלוגית עם קלט לפין 8 ו- PGA עם רווח x1. פלט ADC INT עובר הן להיגיון השעון של SPI והן למטריקס 1 דרך יציאה P0, שם הוא ישמש כאות השעון של המונה המיושם.

יציאות נתונים מקבילות של ADC ו- SPI מסומנות בהתאמה NET11 ו- NET15 כדי להתחבר לרכיב DCMP ב- Matrix1.

שלב 6: תצורת התקנים - לוגיקת שעון SPI

כפי שצוין בעבר בסעיף "יישום לוגיקה", מאגר SPI Buffer מתעדכן בכל פעם שהשוואה בין הערך המאוחסן בפועל לנתוני ההמרה החדשים של ADC יוצרת דופק ביציאת DCMP OUT+.

תקינות האות מובטחת אם אות זה מופעל על ידי יציאת ADC INT. זה מונע כל זינוק והפעלת שווא.

כמו כן הדגשנו כי כדי לדלג על מצבים של מבוי סתום, יש לעדכן את מאגר SPI כאשר הלולאה מגיעה לנתוני הזוכים בפועל.

שלושה אותות נמצאים במשחק לשעון תקין של SPI:

1. יציאת ADC INT (LUT0-IN1)

2. פלט DCMP OUT+ (LUT0-IN0 דרך יציאה P10)

3. הספירה שווה לאות תפס (LUT0-IN2 דרך יציאה P11)

שני הראשונים הם AND-ed ושניהם OR-ed עם האחרונים ב- LUT0, שיישומה מוגדר כמו באיור 6.

שלב 7: תצורת התקנים - מאפייני רכיבי Matrix0

האיורים 7-10 מציגים את שאר חלונות המאפיינים של הרכיבים השייכים ל- Matrix0.

שלב 8: תצורת התקנים - מעגל Matrix1

שלב 9: תצורת התקנים - מונה בינארי 3 סיביות

החלק העליון של המעגל מכיל רכיבי לוגיקה, בעיקר מונה בינארי 3 סיביות שעון פלט ה- ADC INT, כפי שכבר נדון. מונה זה מיושם עם סכמטי די "סטנדרטי" המוצג באיור 12.

מונה זה מתממש בעיצוב שלנו באמצעות כפכפים DFF9, DFF10, DFF11 ו- INV1, LUT4, LUT8. פלט DFF9 הוא ה- LSB ואילו DFF11 הוא ה- MSB כפי שמוצג באיור 13.

LUT4 מוגדר כ- XOR ואילו LUT8 מבצע את ההיגיון AND-XOR של איור 12.

יציאות מונה עוברות לשלושה סיכות פלט דיגיטליות כדי לטפל בכפול אנלוגי חיצוני.

LUT10 מפענח את קוד המונה בסיום הסריקה ומזין דופק ל- Matrix0 באמצעות DLY8 ויציאה P12. זה פשוט מושג על ידי AND-ing של יציאות המונה, ובכך מפענח את המספר 7 dec (0b111 בינארי, סוף הלולאה).

שלב 10: תצורת התקנים - היגיון השוואת 3 סיביות

איור 15 מציג את המעגל המשמש לזיהוי כאשר הלולאה חוזרת על כתובת "הזוכה" הנוכחית. במקרה זה, כפי שכבר נדון, דופק דיגיטלי אמור לאלץ טעינה מחדש של תוצאת ה- ADC הנוכחית כדי לפתור מצב סתום אפשרי.

כתובת "הזוכה" מאוחסנת ברישום הזמני של מטריקס 1 (ראה להלן), בעוד שהכתובת הנוכחית מופקת על ידי המונה הבינארי.

שערי XNOR מספקים פלט אמיתי (לוגיקה 1 או 'גבוהה') כאשר שתי התשומות שוות. AND-ing של האות הזה עבור כל הביטים (LUT9) נותן לנו דופק כאשר שני הקודים הבינאריים זהים. פרטים על שערי XOR כבודק זוגיות ניתן למצוא ב Reference.

האות 'Counter-equals-Latch' מועבר למטריקס 0 דרך יציאה P11.

שלב 11: תצורת מכשירים - היגיון השוואות דיגיטליות ורישום זמני

החלק התחתון של איור 11 (מודגש באיור 16) מציג את בלוק ה- DCMP, חלק קבלת ההחלטות בעיצוב זה.

DFF6, 7 ו- 8 יוצרים רישום של 3 סיביות לאחסון מספר הזנה הזמני "מנצח" בזמן שהלולאה פועלת. קלט לכפכפים הם יציאות הנגד הבינאריות של 3 סיביות, כפי שניתן לראות במעגל הגלובלי של מטריקס 1 באיור 11, כאן דילגו למען הבהירות.

תפוקות מרשם זה אינן יכולות להניע ישירות את התצוגה בת 7 המגזרים מכיוון שהערך המאוחסן כאן משתנה במהלך סריקה ויש לראותו כ'תוקף 'רק בסוף הסריקה עצמה.

מסיבה זו, יציאות הרישום הזמני מתחברות לרשם הלולאה של Matrix0 באמצעות יציאות בין מטריצות P13, P14 ו- P15.

חשוב להבחין באיור 16 שהרשם הזמני נעון על ידי פלט DCMP OUT+ כאשר תוצאות ההשוואה של ADC-SPI רושמות מקסימום חדש שנמצא.

אותו אות OUT+ מועבר ל- Matrix0, SPI CLK Logic, דרך יציאה P10.

שלב 12: תצורת התקנים - מאפייני רכיבי Matrix1

האיורים 17-19 מראים את חלונות המאפיינים של הרכיבים השייכים ל- Matrix1.

שלב 13: תוצאות

כדי לבדוק את היישום, נבנה אב -טיפוס של לוח הערכה, בו מתקבלות 8 מתח הכניסה האנלוגי על ידי סדרת מפרידי הנגדים עם TrimPots (כפי שמוצג באיור 20).

המכפיל המשמש הוא ADG508, חלק שיכול לפעול עם אספקה יחידה (12 וולט).

מנהל התצוגה של 7 פלחים הוא 74LS47. הוא מפענח מילת קלט מקבילה ומניע ישירות תצוגת 7-קטע של אנודה משותפת.

ללוח הערכה יש מחבר 2x10 בזווית ישרה לחיבור ישיר לפלטפורמת פיתוח מתקדם של GreenPAK במחבר ההרחבה שלו כפי שמוצג באיור 21.

השילוב עם פלטפורמת הפיתוח המתקדם של GreenPAK מקל מאוד לבצע מדידות של האותות לבדיקה מהירה. לדוגמה, איור 22 מציג קבוצת אותות (בהתאמה CLOCK, פלט ADC INT ופלט DCMP OUT+) כפי שנלכדו על ידי מנתח לוגי של HP 54620A. צורות גל מופעלות על ידי קצה עולה של אות OUT+ (בהיקף שכותרתו 'A> B'), ומכאן שזוהי לכידת צורת גל כאשר מתגלה מתח מקסימלי חדש בין הכניסות האנלוגיות. למעשה, הוא התקבל על ידי סיבוב אחד TrimPots של לוח הערכה כדי להגדיל את המתח המתאים המוצג באיור 22.

איור 23 מציג את התרשים של לוח ההערכה.

סיכום

במדריך זה יישמנו מאתר מתח מקסימלי (או דק) של שמונה ערוצים שישמש כתוספת נפוצה למערכות בקרה מרובת-ערוצים. הגישה המוצגת מנצלת תכונות מתקדמות של רכיבי GreenPAK ומראה כיצד ניתן להשתלב בפונקציות אנלוגיות ודיגיטליות של שבב אחד. ניתן להחליף מספר מסחרי IC מסחריים ב- Dialog GreenPAKs כך שניתן להקטין את גודל היישום ואת העלות.

מוּמלָץ:

ממיר מתח DC למטה מתח מתח DC (LM2576/LM2596): 4 שלבים

DC-מתג הורדת מתח למטה Buck ממיר מתח באק (LM2576/LM2596): הכנת ממיר באק יעיל ביותר היא עבודה קשה ואפילו מהנדסים ותיקים דורשים עיצובים מרובים כדי להגיע לאחד הנכון. ממיר באק (ממיר הורדה) הוא ממיר מתח DC-to-DC, שמוריד את המתח (תוך הגברת

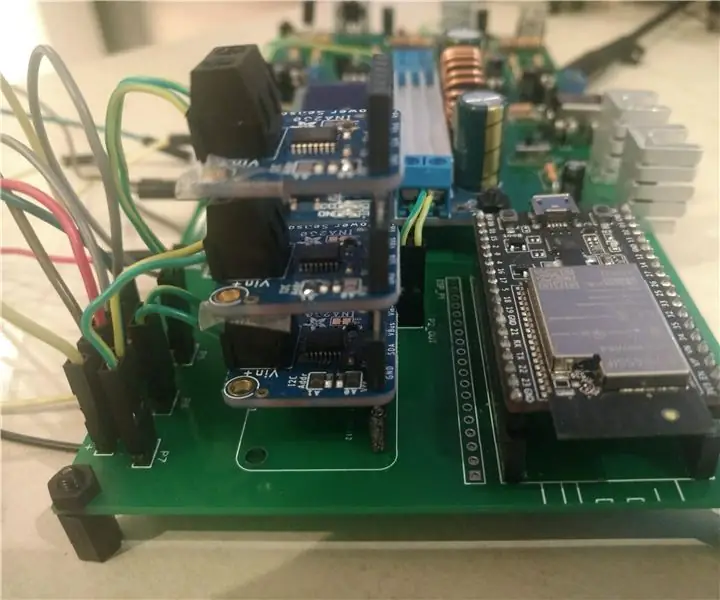

מד מתח וזרם Wifi מרובי ערוצים: 11 שלבים (עם תמונות)

מד מתח וזרם Wifi רב-ערוצי: בעת לוח, יש לעתים קרובות לעקוב אחר חלקים שונים של המעגל בבת אחת. כדי להימנע מהכאב להדביק את בדיקות המולטימטר ממקום למקום, רציתי לעצב מד מתח וזרם רב ערוצי. לוח Ina260

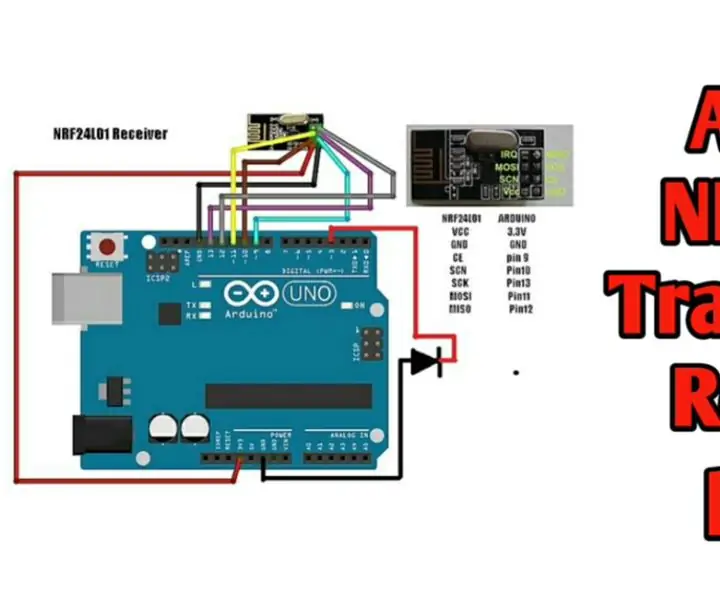

שלט אלחוטי באמצעות מודול NRF24L01 2.4Ghz עם Arduino - Nrf24l01 מקלט משדר 4 ערוצים / 6 ערוצים עבור Quadcopter - מסוק RC - מטוס RC באמצעות Arduino: 5 שלבים (עם תמונות)

שלט אלחוטי באמצעות מודול NRF24L01 2.4Ghz עם Arduino | Nrf24l01 מקלט משדר 4 ערוצים / 6 ערוצים עבור Quadcopter | מסוק RC | מטוס RC באמצעות Arduino: להפעלת מכונית RC | Quadcopter | מזל"ט | מטוס RC | סירת RC, אנחנו תמיד צריכים מקלט ומשדר, נניח שבשביל RC QUADCOPTER אנחנו צריכים משדר ומקלט של 6 ערוצים והסוג הזה של TX ו- RX יקר מדי, אז אנחנו הולכים להכין אחד מהם

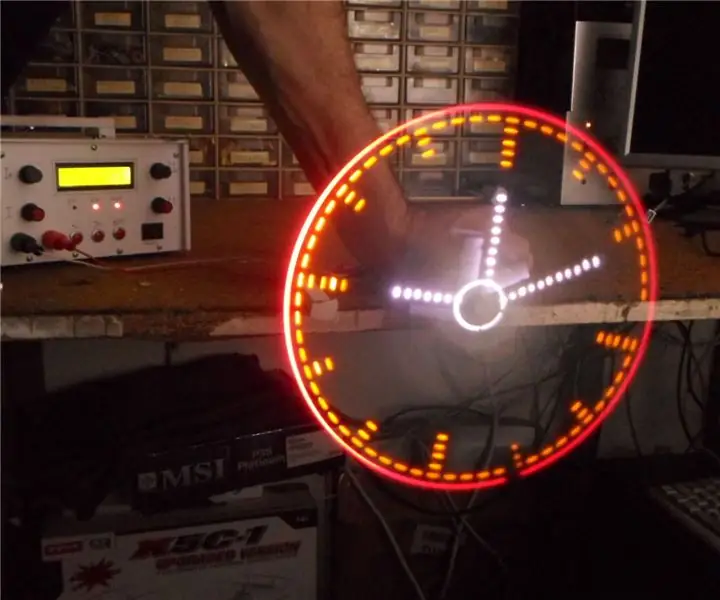

שעון POV Led אנלוגי בסגנון אנלוגי עם Arduino Nano: 4 שלבים

שעון POV LED בסגנון אנלוגי עם Arduino Nano: זה נראה נחמד בעיצוב אנלוגי בסגנון שעון POV

מגבר אנלוגי 8 ערוצים למחשב או בית תיאטרון: 12 שלבים (עם תמונות)

מגבר אנלוגי 8 ערוצים למחשב או HomeTheater: זהו ההנחיה הראשונה שלי. אני אלמד אותך כיצד להכין מגבר בעל 8 ערוצים למחשב או למערכת שמע עם יציאות אנלוגיות נפרדות, השתמשתי בו למחשב השולחני שלי, לצפות בסרטים, להאזין למוסיקה באיכות HD ולשחק משחקים, בנוסף