- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:14.

- שונה לאחרונה 2025-01-23 14:46.

אני כותב את זה מובן מאליו, כי התקשיתי קצת לקבל קוד VHDL התייחסות ללמוד ולהתחיל לעצב בקר מטמון. אז עיצבתי בעצמי בקר מטמון מאפס, ובדקתי אותו בהצלחה ב- FPGA. הצגתי כאן בקר מטמון פשוט ממופה ישיר, כמו גם דגם של מערכת מעבד-זיכרון שלמה לבדיקת בקר המטמון. אני מקווה שאתם מוצאים את ההנחיה שימושית כהפניה לעיצוב בקרי מטמון משלכם.

שלב 1: מפרטים

אלה המפרט העיקרי של בקר המטמון שאנו הולכים לעצב:

- מיפוי ישיר. (עבור לקישור זה אם אתה מחפש בקר מטמון אסוציאטיבי)

- מטמון חד-בנקאי וחוסם.

- מדיניות כתיבה על להיטי כתיבה.

- הקצאת No-Write הקצאה או כתיבה מסביב לגבי פספוס כתיבה.

- ללא מאגר כתיבה או אופטימיזציות אחרות.

- מערך התגים משולב.

חוץ מזה, אנו נעצב גם זיכרון מטמון ומערכת זיכרון ראשית.

מפרטי ברירת המחדל (הניתנים להגדרה) של זיכרון המטמון:

- 256 בייט מטמון חד בנקאי.

- 16 קווי מטמון, כל שורת מטמון (בלוק) = 16 בתים.

המפרט של הזיכרון הראשי:

- זיכרון סינכרוני קריאה/כתיבה.

- זיכרון רב -בנקאי משולב - ארבעה בנקים לזיכרון.

- כל גודל בנק = 1 KB כל אחד. מכאן שהגודל הכולל = 4 kB.

- זיכרון הניתן להתייחסות ל- Word (4 בתים) עם אוטובוס כתובות של 10 סיביות.

- רוחב פס גבוה יותר לקריאה. קרא את רוחב הנתונים = 16 בתים במחזור שעון אחד.

- כתוב רוחב נתונים = 4 בתים.

הערה: בדוק את ההוראה החדשה שלי אם אתה מחפש עיצוב בקר מטמון אסוציאטיבי 4-כיווני

שלב 2: תצוגת RTL של המערכת כולה

ייצוג RTL מלא של המודול העליון מוצג באיור (לא כולל המעבד). מפרטי ברירת המחדל של האוטובוסים הם:

- כל אוטובוסי הנתונים הם אוטובוסים של 32 סיביות.

- אוטובוס כתובת = אוטובוס 32 סיביות (אך ניתן להזמין כאן רק 10 סיביות לפי הזיכרון).

- בלוק נתונים = 128 סיביות (אוטובוס רחב רוחב לקריאה).

- כל הרכיבים מונעים על ידי אותו שעון.

שלב 3: סביבת בדיקה

המודול העליון נבדק באמצעות ספסל בדיקה, שמדגם פשוט מעבד שאינו צינורי (כי עיצוב מעבד שלם כלל לא פשוט !!). ספסל הבדיקה יוצר בקשות נתוני קריאה/כתיבה לזיכרון לעתים קרובות. זה לועג להוראות טיפוסיות של "Load" ו- "Store", הנפוצות בכל התוכניות המבוצעות על ידי מעבד. תוצאות הבדיקה אימתו בהצלחה את הפונקציונליות של בקר המטמון. להלן נתוני הבדיקה שנצפו:

- כל האותות קריאה/כתיבה של החמצה ופגיעה נוצרו בצורה נכונה.

- כל פעולות נתוני קריאה/כתיבה הצליחו.

- לא זוהו בעיות אי עקביות/עקביות של נתונים.

- העיצוב אומץ בהצלחה לתזמון עבור מקסימום. תדירות הפעולה של השעון = 110 מגהרץ בלוח Xilinx Virtex-4 ML-403 (מערכת שלמה), 195 מגהרץ לבקר מטמון בלבד.

- זיכרונות בלוק הוסקו עבור הזיכרון הראשי. כל המערכים האחרים יושמו על LUTs.

שלב 4: קבצים מצורפים

הקבצים הבאים מצורפים כאן עם הבלוג הזה:

- קבצי VHD של בקר מטמון, מערך נתוני מטמון, מערכת זיכרון ראשית.

- מבחן ביצועים.

- תיעוד על בקר המטמון.

הערות:

- עיין בתיעוד להבנה מלאה של המפרטים של בקר המטמון המוצג כאן.

- כל שינויים בקוד תלויים במודולים אחרים. לכן, השינויים צריכים להיעשות בשיקול דעת. שימו לב לכל ההערות והכותרות שנתתי.

- אם מסיבה כלשהי, לא ניתן להסיק זיכרון RAM לחסימה עבור הזיכרון הראשי, הפחת את גודל הזיכרון, ואחריו שינויים ברוחבי אוטובוס הכתובות על פני הקבצים וכן הלאה. כך שניתן ליישם את אותו הזיכרון ב- LUT או ב- RAM מבוזר. זה יחסוך את זמן הניתוב והמשאבים. לחלופין, עבור אל תיעוד ה- FPGA הספציפי ומצא את הקוד התואם לבלוק RAM וערוך את הקוד בהתאם, והשתמש באותו מפרטי רוחב אוטובוס כתובת. אותה טכניקה עבור FPGA של Altera.

מוּמלָץ:

שעון ניקסי עם ארדואינו - עיצוב פשוט ביותר: 4 שלבים

שעון ניקסי עם ארדואינו | עיצוב פשוט ביותר: לאחר יום עבודה ארוך, סוף סוף הצלחתי לייצר שעון ניקסי עם ארדואינו ושבב בידוד אופטי, אין צורך בדרייבר של ניקסי שקשה לרכוש אותו

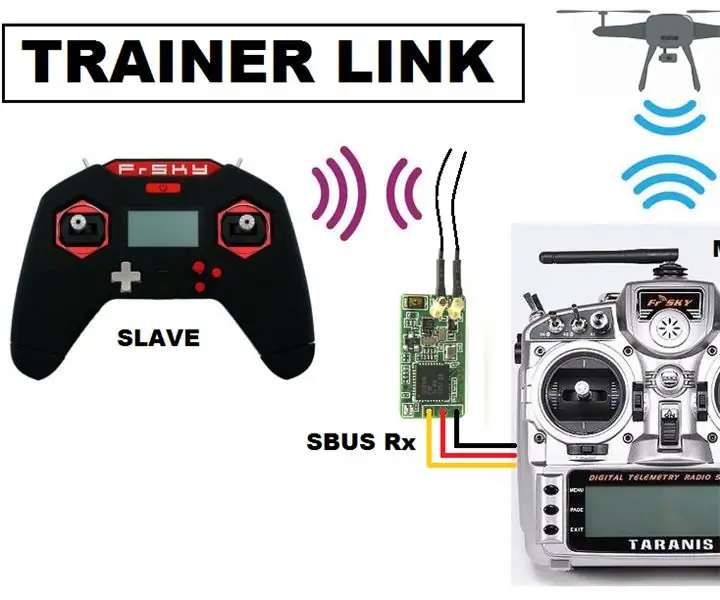

מאמן Taranis X9D+ פשוט פשוט באמצעות קלט מקלט SBUS: 9 שלבים

פשוט Taranis X9D+ מאמן אלחוטי באמצעות קלט מקלט SBUS: מטרת הפרויקט היא לחבר משדר FrSky X-Lite למשדר FrSky X9D+ בתצורת TRAINER באמצעות מקלט SBUS זול (12 $). על ידי חיבור השניים בצורה זו, אפשר לטייס מדריך באמצעות

עיצוב לוח פיתוח מיקרו -בקר: 14 שלבים (עם תמונות)

תכנון לוח פיתוח מיקרו -בקר: האם אתה יוצר, חובב או האקר המעוניין להתגבר מפרויקטים של פרפבורד, מכשירי DIP ומחשבי PCB תוצרת בית למחשבי PCB מרובי שכבות המיוצרים על ידי בתי לוח ואריזות SMD מוכנות לייצור המוני? אז ההנחיה הזו היא בשבילך! הגוי הזה

כיצד להרכיב בקר ידית פשוט ועוצמתי- מבוסס על המיקרו: ביט: 10 שלבים (עם תמונות)

כיצד להרכיב בקר ידית פשוט ועוצמתי- מבוסס על המיקרו: ביט: שם הידית הוא Handlebit. הצורה היא ידית והיא נראית מגניבה מאוד! עכשיו נוכל לערוך הקדמה אודות ה- Handlebit, בואו נעבור עליה

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: 9 שלבים

עמדת הטיה למגבר גיטרה - עיצוב "כיסא אפריקאי" - פשוט, קטן, חזק, קל, חינם או ממש זול: מעמד הטיה למגבר גיטרה - קל מדי - פשוט, קטן, חזק, חינם או ממש זול. לכל אמפר בכל גודל, אפילו ארונות גדולים עם ראש נפרד. פשוט צור לוחות וצינורות בגודל ואתה צריך כמעט לכל ציוד שאתה רוצה