תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:12.

- שונה לאחרונה 2025-01-23 14:46.

מאת AmCoder https://www.linkedin.com/in/mitu עקוב אחר המחבר:

אודות: Mitu Raj - רק תחביב ולומד - מעצב שבבים - מפתח תוכנה - חובב פיזיקה ומתמטיקה עוד על AmCoder »

## זהו הקישור הפופולרי ביותר בלחיצה ב- Google ליישום VHDL של CORDIC ALGORITHM ליצירת גל סינוס וקוסינוס ## כיום קיימים אלגוריתמים יעילים בחומרה רבים, אך אלה אינם ידועים היטב בשל הדומיננטיות של מערכות תוכנה על השנים הרבות. CORDIC הוא אלגוריתם כזה שאינו אלא קבוצה של shift ו- add logics המשמשים לחישוב מגוון רחב של פונקציות כולל פונקציות טריגונומטריות, היפרבוליות, לינאריות ולוגריתמיות. זהו האלגוריתם המשמש במחשבונים וכו '. על ידי שימוש בשיפטים ותוספים פשוטים אנו יכולים לעצב חומרה עם פחות מורכבות אך עוצמה של DSP באמצעות אלגוריתם כבל. מכאן שניתן לעצב אותו כעיצוב RTL חשוף ב- VHDL או Verilog ללא שימוש ביחידות נקודה צפות ייעודיות או IP מורכבות מתמטיות.

שלב 1: VHDL ומודלסים

כאן האלגוריתם הקורי מיושם באמצעות VHDL ליצירת גל סינוס וגל קוז. זה יכול להוציא סינוס וקוסינוס של זווית קלט בדיוק רב. הקוד ניתן לסינתזה ב- FPGA. מודלים משמשים לדמות העיצוב וספסל הבדיקה.

שלב 2: קוד VHDL לעיצוב ולספסל הבדיקה

טכניקת קנה מידה בינארי משמשת לייצוג מספרי נקודות צף.

אנא עיין במסמכים המצורפים לפני שאתה מקודד.

עבור דרך סימולציה של cordic_v4.vhd - העיצוב -הקלט הוא זווית ב 32 סיביות + סימן ביט; זה יכול לעבד כל זווית מ 0 ל +/- 360 מעלות עם דיוק קלט של 0.000000000233 תואר. כאשר נותנים קלט -> MSB הוא סימן הסימן והשאר 32 סיביות מייצגות גודל. -פלט העיצוב הוא ערך הסינוס והקוס שלו ב -16 סיביות + סימן ביט. עם דיוק 0.00001526. שים לב שהפלט מוצג בצורת מחמאה של 2 אם ערך הסינוס או cos בהתאמה שלילי. הדמיה של testb.vhd - ספסל מבחן לעיצוב (1) זוויות קלט ואיפוס משיכה = '0'. לאחר שני שלבים של סימולציה, משוך את האפס ל- '1' ו"הפעל הכל ". (2) בחלון הסימולציה הגדר את רדיקל החטא והקוס כפי שהוא עשרוני ופורמט> אנלוגי (אוטומטי). (3) התקרב כדי לראות את צורת הגל כראוי.

שלב 3: קבצים מצורפים

(1) cordic_v4.vhd - עיצוב. (2) testb.vhd - ספסל בדיקה לעיצוב.

(3) מסמך כיצד לאלץ כניסות זווית ולהמיר את התוצאות הבינאריות.

עדכון: קבצים אלה נשמרים ואינם מסופקים יותר. אנא השתמש בקבצים מהשלב הבא

שלב 4: ליבת IP מיני -קורדיק - 16 ביט

המגבלה של ההטמעה לעיל היא- תדירות הפעולה האיטית והנמוכה של השעון בגלל ביצוע חישובים במחזור שעון יחיד. Core Mini-Cordic IP- 16 ביט

- נתיבים קריטיים המופצים למספר מחזורים לשיפור הביצועים.- מהיר יותר- עיצוב מוכח FPGA מסונתז עד שעון 100 מגה-הרץ.- שטח אופטימיזציה נוספת ב- HDL, חומרה פחותה.- אותות מצב עומס ונעשה נוספו. הקודם.

אוטומטית לחלוטין מכניסות זווית 0 עד 360 מעלות

קבצים מצורפים: 1) קובץ vhdl ראשי מיני קורדי 2) ספסל בדיקה מיני קורדי 3) מדריך מיני קורדי IP ליבה 4) דוק כיצד לכפות זוויות ולהמיר תוצאות

לכל שאלה אתה מוזמן לפנות אלי:

מיטו ראג '

עקוב אחריי:

דואר: iammituraj@gmail.com

### סך כל ההורדות: 325 עד 01-05-2021 ###

### הקוד נערך לאחרונה: 07-2020 ביולי ###

מוּמלָץ:

רובוט איזון עצמי - אלגוריתם בקרת PID: 3 שלבים

רובוט איזון עצמי - אלגוריתם בקרת PID: פרויקט זה נבנה כי התעניינתי ללמוד עוד על אלגוריתמי בקרה וכיצד ליישם לולאות PID פונקציונליות ביעילות. הפרויקט עדיין בשלבי פיתוח מכיוון שטרם הוסיף מודול בלוטות 'אשר יביא

רובוט איזון עצמי באמצעות אלגוריתם PID (STM MC): 9 שלבים

רובוט איזון עצמי באמצעות אלגוריתם PID (STM MC): לאחרונה נעשתה עבודה רבה באיזון עצמי של אובייקטים. הרעיון של איזון עצמי החל באיזון של מטוטלת הפוכה. תפיסה זו הורחבה גם לעיצוב מטוסים. בפרויקט זה, עיצבנו מוד קטן

Tic Tac Toe ב- Arduino עם AI (אלגוריתם מינימקס): 3 שלבים

Tic Tac Toe על Arduino עם AI (אלגוריתם מינימקס): במדריך זה אני הולך להראות לך כיצד לבנות משחק Tic Tac Toe עם AI באמצעות Arduino. אתה יכול לשחק נגד הארדואינו או לצפות בארדואינו משחק נגד עצמו. אני משתמש באלגוריתם שנקרא "אלגוריתם מינימקס"

שלוט בארדואינו באמצעות סמארטפון באמצעות USB באמצעות אפליקציית Blynk: 7 שלבים (עם תמונות)

שליטה בארדואינו באמצעות סמארטפון באמצעות USB באמצעות אפליקציית Blynk: במדריך זה נלמד כיצד להשתמש באפליקציית Blynk ובארדואינו על מנת לשלוט במנורה, השילוב יהיה באמצעות יציאה טורית USB. מטרת ההוראה היא להראות את הפתרון הפשוט ביותר לשלוט מרחוק בארדואינו או ב

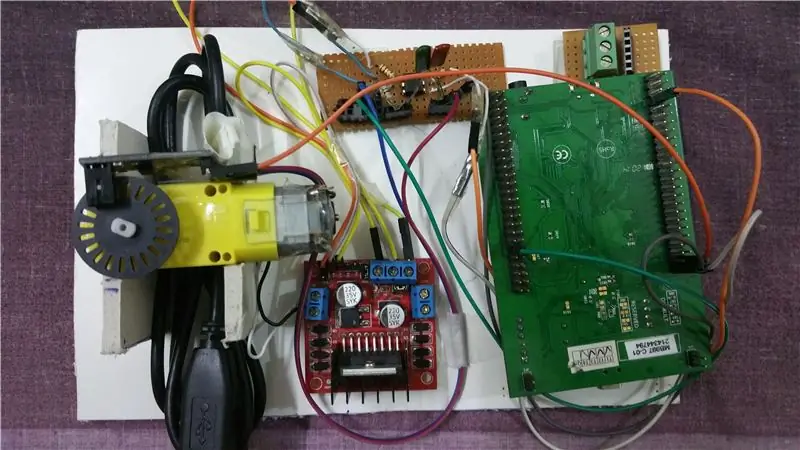

בקרת מהירות של מנוע DC באמצעות אלגוריתם PID (STM32F4): 8 שלבים (עם תמונות)

בקרת מהירות של מנוע DC באמצעות אלגוריתם PID (STM32F4): שלום לכולם, זהו tahir ul haq עם פרויקט אחר. הפעם זה STM32F407 בתור MC. זהו פרויקט סוף אמצע סמסטר. מקווה שאתה אוהב את זה. זה דורש הרבה מושגים ותיאוריה אז אנחנו נכנסים לזה קודם. עם הופעת המחשבים ו