תוכן עניינים:

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:15.

- שונה לאחרונה 2025-01-23 14:46.

במדריך זה אנו הולכים לעצב מאסטר SPI Bus מאפס ב- VHDL.

שלב 1: סקירה כללית של SPI

- SPI הוא אוטובוס סדרתי סינכרוני

- הפופולריות והפשטות שלו הפכו אותו לסטנדרט בפועל בתקשורת הסדרתית

- אוטובוס בדופלקס מלא

- פרוטוקול פשוט ובין האוטובוס הטורי המהיר ביותר

שלב 2: מפרט עיצוב

אלה המפרט של ה- SPI Master שאנו מתכננים לעצב:

- תומך בכל ארבעת דרכי הפעולה; ניתנת להגדרה דינאמית

- שעון מאפשר שליטה לחיסכון בחשמל

- אורך ומהירות מילה הניתנת להגדרה סטטית

- הפרעה יחידה הן לשידור והן בקבלה

שלב 3: התחלה

קודם כל, ה- IP שלנו צריך להיות בעל שני ממשקים. האחד הוא ממשק סידורי והשני הוא ממשק מקביל. הממשק הטורי מורכב מהאותות הסטנדרטיים דה-פקטו של SPI: MOSI, MISO, SS, SCLK.

MOSI נקרא לפעמים SDO ו- MISO נקרא לפעמים SDI.

ממשק סידורי משמש לתקשורת עם ציוד היקפי חיצוני, כלומר עבדי SPI.

ממשק מקביל משמש לתקשורת עם המארח שלנו, כלומר, מיקרו -בקר או מיקרו -מעבד, שאומר למעשה למאסטר אילו נתונים יש להעביר באופן סדרתי ולקבל דרך הקווים הטוריים. כלומר, כל אוטובוסי הנתונים שייכים לממשק מקביל.

יש לנו שעון גלובלי שמניע את ההיגיון SPI הפנימי, כמו גם את SCLK, אותו אנו מייצרים באופן פנימי.

יש לנו גם כמה אותות בקרה כמו כתיבת הפעלה, הפעלת שעון. וקטעי אותות סטטוס אחרים.

מכיוון שעלינו להתמודד עם תנאי בקרה מורכבים, פשוט יותר לתכנן כתובות IP תקשורתיות טוריות כ- FSM. אנו נעצב את SPI master גם כ- FSM. ה- FSM יונע על ידי שעון פנימי אחר שהוא פי SCLK. שעון פנימי זה נוצר באמצעות מונים סינכרוניים מהשעון הגלובלי.

לכל אותות הבקרה שחוצים תחומי שעון יש מסנכרים שיהיו בצד הבטוח יותר.

שלב 4: תצוגת RTL של ליבות הליבה הראשיות של SPI וצורות גל סימולציה

זהו עיצוב RTL חשוף ללא שימוש ב- IPS FPGA ייעודי. מכאן שהוא קוד נייד לחלוטין לכל FPGA.

מוּמלָץ:

עיצוב מתנד מבוסס מצב נוכחי למגברי הספק אודיו מסוג D: 6 שלבים

עיצוב אוסילטור מבוסס מצב נוכחי למגברי כוח שמע D: בשנים האחרונות הפכו מגברי הסאונד מסוג D לפתרון המועדף על מערכות שמע ניידות כמו MP3 וטלפונים ניידים בשל יעילותם הגבוהה וצריכת החשמל הנמוכה. המתנד הוא חלק חשוב ממחלקה D au

עיצוב משחק בקפיצה ב -5 שלבים: 5 שלבים

עיצוב משחק בקפיצה ב -5 שלבים: פליק הוא דרך פשוטה מאוד ליצור משחק, במיוחד משהו כמו פאזל, רומן חזותי או משחק הרפתקאות

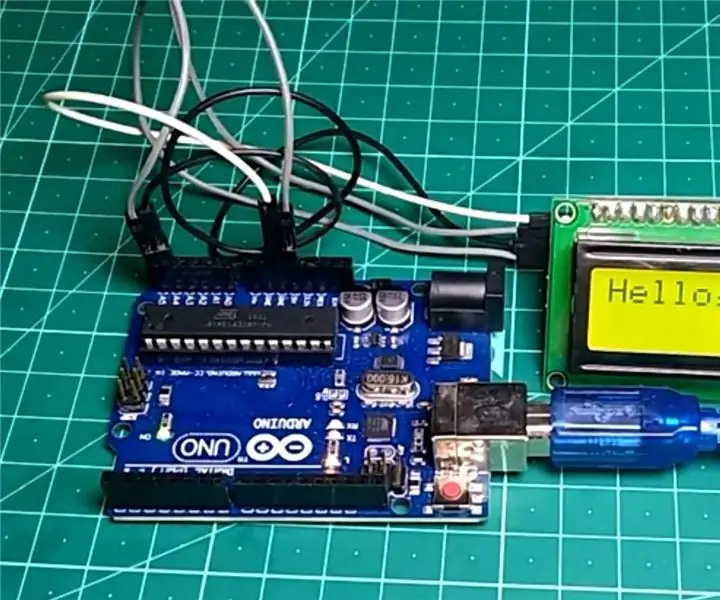

תצוגת LCD I2C / IIC - השתמש ב- LCD SPI לתצוגת LCD I2C באמצעות מודול SPI ל- IIC עם Arduino: 5 שלבים

תצוגת LCD I2C / IIC | השתמש ב- LCD SPI לתצוגת LCD I2C באמצעות מודול SPI ל- IIC עם Arduino: היי חבר'ה מכיוון של- SPI LCD 1602 רגיל יש יותר מדי חוטים להתחבר כך שקשה מאוד לחבר אותו ל- arduino אבל יש מודול אחד זמין בשוק שיכול המר את תצוגת SPI לתצוגת IIC, אז עליך לחבר רק 4 חוטים

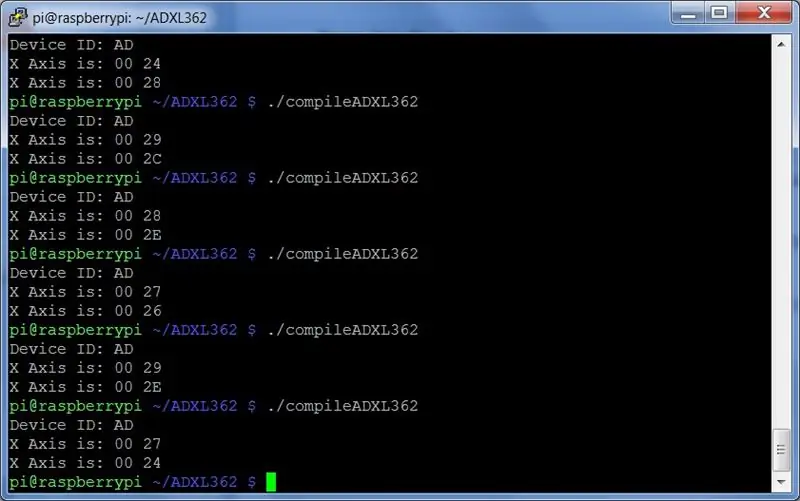

מקדים* SPI ב- Pi: תקשורת עם מד תאוצה 3 צירים SPI באמצעות פטל פטל: 10 שלבים

מקדים* SPI ב- Pi: תקשורת עם מד תאוצה 3 צירים באמצעות SPI באמצעות פטל פטל: מדריך שלב אחר שלב כיצד להתקין את Raspbian ולתקשר עם מכשיר SPI באמצעות ספריית SPM bcm2835 (לא חבטה קצת!) זה עדיין מאוד ראשוני … אני צריך להוסיף תמונות טובות יותר של חיבור פיזי ולעבוד על חלק מהקוד המביך

עיצוב PCB עם שלבים פשוטים וקלים: 30 שלבים (עם תמונות)

עיצוב PCB עם שלבים פשוטים וקלים: שלום חברים הדרכה שימושית וקלה מאוד למי שרוצה ללמוד עיצוב PCB בוא נתחיל