תוכן עניינים:

- שלב 1: בניית מודול PWM- קובץ מקור

- שלב 2: בניית מודול PWM- התקנת Vivado

- שלב 3: בניית מודול PWM- צור קובץ פרוייקט

- שלב 4: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (I)

- שלב 5: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (II)

- שלב 6: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (III)

- שלב 7: בניית מודול PWM- עיצוב בלוק והגדרת קובצי אילוץ (IV)

- שלב 8: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (V)

- שלב 9: בניית מודול PWM- התקנת חומרה

- שלב 10: בניית מודול PWM- צור Bitstream והפעל SDK

- שלב 11: בניית מודול PWM- צור יישום חדש ב- Xilinx SDK

- שלב 12: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (I)

- שלב 13: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (II)

- שלב 14: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (III)

- שלב 15: בניית מודול PWM- סיכום פונקציית PWM (I)

- שלב 16: בניית מודול PWM- סיכום פונקציית PWM (II)

- שלב 17: בניית מודול PWM- סיכום פונקציית PWM (III)

- שלב 18: בניית מודול PWM- הפעל אותו

- שלב 19: הזרמת עיבוד וידאו ב- Digilent ZYBO עם OV7670

- שלב 20: תרשים בלוק מלא

- שלב 21: חבר את ה- OV7670 ל- ZYBO

- שלב 22: צור עיצוב בלוק

- שלב 23: הוסף קבצי VHDL לשליטה ולכידה במצלמות OV7670

- שלב 24: הוסף קובץ אילוצים

- שלב 25: הוסף IP Repo עבור HLS IP

- שלב 26: הוסף מודולים ו- IP

- שלב 27: הגדרות תצורת IP

- שלב 28: הוסף והגדר את בלוק ה- IP של PS

- שלב 29: חלק 1. בניית מודול PWM עבור מנועי סרוו

- שלב 30: חיבורי צד של קלט וידאו (aclk מודגש)

- שלב 31: חיבורים ל- OV7670

- שלב 32: חיבורים בצד הווידאו החוצה

- שלב 33: הפעל אוטומציה של בלוק וחיבורים

- שלב 34: צור עטיפת HDL

- שלב 35: צור Bitstream, ייצא חומרה ל- SDK, הפעל SDK מ- Vivado

- שלב 36: SDK (ללא FreeRTOS)

- שלב 37: יישום FreeRTOS

- שלב 38: הוראות שימוש

- שלב 39: הפניות וקישורים

- מְחַבֵּר John Day day@howwhatproduce.com.

- Public 2024-01-30 09:17.

- שונה לאחרונה 2025-01-23 14:46.

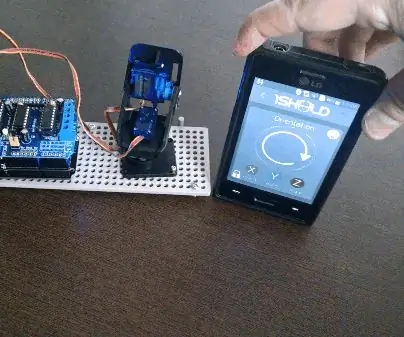

התחל בשלב הראשון לפרטים על יצירת בקר PWM סרוו בעל 2 צירים.

התחל בתרשים הבלוק המאסיבי (שלב 19) לפרויקט המלא.

מצלמה + הגדרת פאן/הטיה בה השתמשנו:

ה- PmodCON3 מ- Digilent שימש לחיבור הסרווואים.

שלב 1: בניית מודול PWM- קובץ מקור

שלב 2: בניית מודול PWM- התקנת Vivado

ראשית, הורד את אתר Vivado Design Suite מאת Xilinx. התקן את כל חבילת העיצוב, כולל ערכת פיתוח תוכנה של Vivado (SDK). פרויקט זה משתמש בגרסת 2017.2.

בינתיים, Digilent Adept 2 צריך להיות מותקן גם כנהג לוח Zybo.

שלב 3: בניית מודול PWM- צור קובץ פרוייקט

לפני יצירת קובץ פרוייקט, עליך לוודא שהתקנת את קובץ ה- Zybo כראוי כהדרכה כאן:

התקנת קובצי לוח גירסה 2015.1 ואילך

פתח את Vivado 2017.2. בהתחלה מהירה, לחץ על צור פרוייקט -> הבא -> שם הפרויקט (שם שם הפרויקט שלך כאן) -> סוג הפרויקט. בסוג פרויקט, בחר פרויקט RTL וסמן על "אל תציין מקורות בשלב זה". לאחר מכן, עבור חלק ברירת המחדל, בחר "לוחות" ו- "Zybo" כשם תצוגה. לאחר מכן, לחץ על סיום כדי להתחיל את הפרויקט.

שלב 4: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (I)

ב- Flow Navigator, לחץ על "" צור עיצוב בלוק "ולאחר מכן הקש על אישור. לחץ על סימן "+" כדי להוסיף כתובות IP נחוצות. לְהוֹסִיף:

- מערכת עיבוד אחת ZYNQ7 שני טיימר AXI

- שני טיימר AXI

שלב 5: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (II)

לאחר הוספת כתובות IP, הפעל את אוטומציה הבלוק ואוטומציה של חיבורים. לאחר השלמת האוטומציה, בלוק "axi_timer_0", לחץ לחיצה ימנית על pwm0 -> צור חיצוני. תן שם לסיכה החיצונית pwm0 כ- pwm_Xaxis. כמו כן, חזור על התהליך לעיל על הבלוק "axi_timer_1" ושם את הסיכה החיצונית pwm0 כ- pwm_Zaxis.

שלב 6: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (III)

שימו לב כי בכל פעם שאנו מסיימים את עיצוב הבלוק ב- Vivado, עלינו ליצור עטיפת HDL. מכיוון שזה יהיה המודול ברמה העליונה עבור כל פרויקט.

שלב 7: בניית מודול PWM- עיצוב בלוק והגדרת קובצי אילוץ (IV)

כעת עלינו להגדיר את קובץ האילוץ שלנו כדי להקצות סיכות המחוברות לתרשים הבלוקים שלנו. סגור את חלון עיצוב הבלוק, בכרטיסיה מקורות, "הוסף מקורות"-> הוסף או צור אילוצים-> הוסף את Zybo-Master.xdc כקבצי האילוץ שלנו.

שלב 8: בניית מודול PWM- עיצוב בלוק והגדרת קובץ אילוץ (V)

פתח את קובץ האילוץ Zybo-Master.xdc מהתיקייה Constraints, בטל את התגובות ליציאות שברצוננו לציין כאותות פלט ושנה את השם "get_ports {XXXX}", ש- XXXX מציין את הסיכה החיצונית בשם בתרשים החסימה. ההגדרה של קובץ האילוץ מוצגת באיור.

שלב 9: בניית מודול PWM- התקנת חומרה

חבר את מנועי הסרוו ל- Pmod CON3. TowerPro SG90 הוא דגם מנוע הסרוו בו השתמשנו בפרויקט זה. עבור חוטי מנוע הסרוו, החוט הכתום מייצג את אות ה- PWM, המחובר לסיכת SIG ב- Pmod CON3. החוט האדום Vcc הוא חוט חשמל המחובר לסיכה VS ב- Pmod CON3. לבסוף, החוט החום Gnd הוא חוט טחון המחובר לסיכת GND. לאחר מכן, הכנס את Pmod CON3 לשורה העליונה של יציאת JD בלוח ה- Zybo.

שלב 10: בניית מודול PWM- צור Bitstream והפעל SDK

1. בכרטיסייה ניווט פרויקטים, הפעל צור BitStream.

2. ייצוא חומרה: קובץ> ייצוא> ייצוא חומרה-> סימון ב- "include bitstream"-> אישור 3. הפעל SDK: קובץ-> הפעל SDK.

שלב 11: בניית מודול PWM- צור יישום חדש ב- Xilinx SDK

צור אפליקציה חדשה:

קובץ> חדש> פרויקט יישומים -> הזן את שם הפרויקט שלך -> סיום

תחת פרויקט סייר, אמורות להיות שלוש תיקיות.

במקרה זה, "design_1_wrapper_hw_platform_0" היא התיקיה שיצאה בעבר על ידי Vivado. Axis_2_PWM_SDK_bsp היא תיקיית חבילת התמיכה בלוח. ו- Axis_2_PWM_SDK היא תיקיית הפרויקטים הראשית שלנו ב- SDK. אתה יכול לראות את הקובץ "helloworld.c" מתחת לתיקייה "src" של Axis_2_PWM_SDK, כאשר "helloworld.c" הוא הקובץ הראשי.

שלב 12: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (I)

בואו לבדוק כמה קבצים תחת סייר הפרויקט. ראשית, בתיקייה "design_1_wrapper_hw_platform_0", פתח את "system.hdf". קובץ זה מדגים את מפת הכתובות של המעבד ps7_cortex9 ואת בלוקי ה- IP הקיימים בעיצוב שלנו.

שלב 13: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (II)

לאחר מכן, בדוק את הקובץ "כלול" ו- "libsrc" תחת התיקיה "Axis_2_PWM_SDK_bsp". קבצי הספרייה כאן מאפשרים לנו לקיים אינטראקציה עם ציוד היקפי לחומרה מבלי "לשחק" רישומים.

שלב 14: בניית מודול PWM- סקירה כללית של סייר הפרויקטים (III)

באמצעות תיעוד BSP, xtmrctr.h נמצא כספריית בקרת טיימר של Xilinx הקשורה ל AXI טיימר. בדרך כלל, נוכל למצוא כאן את הפונקציה הרצויה של PWM. עם זאת, אם אתה קורא את התיעוד "tmrctr_v4_3", הוא מראה כי מנהל ההתקן אינו תומך כעת בפעולת PWM של המכשיר. בשל המחסור בפונקציית PWM, עלינו לסכם את פונקציית ה- PWM שלנו בעזרת מדריך המוצר xtmrctr.h ו- AXI Timer v2.0 LogiCORE.

שלב 15: בניית מודול PWM- סיכום פונקציית PWM (I)

בחזרה לקובץ הראשי "helloworld.c", כלול את קבצי הכותרת הבאים:

שלב 16: בניית מודול PWM- סיכום פונקציית PWM (II)

הגדר את כתובות הבסיס של שני טיימר AXI דרך "xparameters.h".

שלב 17: בניית מודול PWM- סיכום פונקציית PWM (III)

בנה את הפונקציה הרצויה של PWM.

Duty_val: ממיר את ערך התואר למחזור עבודה. PWM_Freq_Duty: הגדר את תדירות ומחזור העבודה הרצוי ליצירת PWM. יש להקצות גם תקופת שעון.

PWM_START: הקצה את כתובת הרישום של PWM והתחל לייצר PWM.

PWM_STOP: הקצה את כתובת הרישום של PWM והפסק לייצר PWM.

שאר קוד ההדגמה מוצג ב- "helloworld.c" תחת "Axis_2_PWM_SDK"

שלב 18: בניית מודול PWM- הפעל אותו

1. לתכנת את ה- FPGA באמצעות SDK

- חבר את לוח Zybo דרך יציאת USB למחשב.

- כלי Xilinx -> תוכנית FPGA

2. הפעל את התוכנית

לחץ על הסמל "הפעלה" ותוריד את התפריט -> הפעל בשם -> הפעל על חומרה

3. מסוף SDK

- פתח את מסוף SDK -> התחבר ליציאה טורית -> אישור

- הפעל את התוכנית. אם קוד ההדגמה פועל בהצלחה, אתה אמור לראות אתחול האתחול בוצע! במסוף SDK.

שלב 19: הזרמת עיבוד וידאו ב- Digilent ZYBO עם OV7670

מצורף קובץ ארכיון מלא.

שלב 20: תרשים בלוק מלא

זה מציג את התרשים המלא של כל החיבורים ובלוקי ה- IP בפרויקט

שלב 21: חבר את ה- OV7670 ל- ZYBO

צור חיבור כדי לחבר את המודול ov7670 ל- ZYBO Pmods

נתונים Pmod הוא Pmod D.

שליטה Pmod היא Pmod C

בנוסף, חבר את ה- PmodCON3 וה- servos כמפורט במחצית הראשונה של מדריך זה

שלב 22: צור עיצוב בלוק

ב- Flow Navigator, לחץ על "צור עיצוב בלוק" ולאחר מכן הקש על אישור.

שלב 23: הוסף קבצי VHDL לשליטה ולכידה במצלמות OV7670

הוסף את קבצי VHDL המצורפים לשלב זה לפרויקט

שלב 24: הוסף קובץ אילוצים

הוסף את קובץ האילוצים המצורף לפרויקט שלך.

שלב 25: הוסף IP Repo עבור HLS IP

קח את קובץ ה- Zip המצורף ופתח אותו לתיקיה חדשה בשם דומה בספרייה חדשה (תיקייה) בשם "HLS_repo".

הוסף מאגר IP לפרויקט שלך על ידי מעבר לקטלוג ה- IP ולחץ באמצעות לחצן העכבר הימני על "הוסף מאגר …"

נווט לספריית "HLS_repo" ובחר אותה.

אופציונלי: צור לעצמך את בלוק עיבוד הווידיאו HLS!

שלב 26: הוסף מודולים ו- IP

הוסף את מודולי ov7670_axi_stream_capture, debounce ו- ov7670_controller לתרשים הבלוקים על ידי לחיצה ימנית על הרקע ובחירה באפשרות "הוסף מודול …"

באופן דומה, הוסף את כתובות ה- IP:

- HLS_Video_Track

- כתיבת מאגר מסגרת וידאו

- מאגר מסגרת וידאו קרא

- בקר תזמון וידאו

- הזרמת AXI4 לווידיאו אאוט

- 3 מתוך "פרוסה"

- קָבוּעַ

- 2 של טיימר AXI

שלב 27: הגדרות תצורת IP

כפי שמוצג בתמונות

שלב 28: הוסף והגדר את בלוק ה- IP של PS

הוסף את מערכת העיבוד ZYNQ7 לתרשים הבלוקים

ערוך את התצורה:

-

תצורת PS-PL

-

HP

- הפעל את S HP 0

- אפשר S HP 1

-

-

הגדרת שעון

-

שעוני בד PL

- FCLK_0 ב 100MHz

- FCLK_1 במהירות 25MHz (OutputClock)

- FLCK_2 ב- 35MHz (<= 50MHz) (CameraClock)

-

שלב 29: חלק 1. בניית מודול PWM עבור מנועי סרוו

הוצא את axi_timer_0 pwm0 ליציאת הפלט החדשה pwm_Xaxis

הוצא את axi_timer_1 pwm0 ליציאת הפלט החדשה pwm_Zaxis

שלב 30: חיבורי צד של קלט וידאו (aclk מודגש)

חבר את בלוקי ה- IP בצד קלט הווידאו כראוי

(* יש ליצור חיבורים אלה על ידי בחירת האפשרויות הנכונות במהלך אוטומציה של חיבורים) "aclk" מתוך axi_stream_capture עובר אל:

- ap_clk על כתיבת מאגר מסגרת וידאו

- ap_clk על בלוק עיבוד זרמי וידאו מסוג HLS

- *aclk ב- AXI smartconnect IP ממאגר מסגרת הווידאו כתוב ל- S_AXI_HP0

- *aclk המתאים לערוצי ה- AXI Interconnect IP עבור ערוצי S_AXI של בלוק עיבוד הווידיאו HLS ומאגר מסגרת הווידיאו כתוב S_AXI_HP0_ACLK על הבלוק PS

אות זרם הווידאו פשוט מחובר בסדרה בין בלוק הלכידה לממשק הזיכרון של Zynq.

- הסרטון עובר מגוש לכידה לבלוק עיבוד HLS.

- הסרטון המעובד מגוש HLS עובר לגוש הכתיבה של מאגר המסגרות.

- *בלוק הכתיבה של מאגר המסגרות מתחבר לממשק HP0 בגוש Zynq PS.

- האות m_axis_tuser מהפלט של בלוק הלכידה מחובר באופן ידני הן לאות הקלט video_in_TUSER בבלוק עיבוד HLS והן לאות ap_start באותו בלוק.

האות TUSER (tuser) משמש את פרוטוקול זרם הווידאו של AXI כדי להצביע על תחילת מסגרת של הווידאו. נכנס כאשר נכנסים אות בודד של אוטובוס ומפצלים אותו בצורה כזו יש צורך לחבר אותו גם לנקודת הסיום הרגילה של שאר האוטובוס. Vivado מניח שאם אתה מחבר את האות באופן ידני שאתה רוצה לנתק את מה שהוא היה מתחבר אליו בדרך כלל.

הגדרות תצורה של בלוקים IP:

כתוב מאגר מסגרת וידאו:

פורמטי וידאו: RGB8

דוגמה אחת לשעון מקסימום עמודות: 1280 (> = 640) שורות מרביות: 960 (> = 480) רוחב נתונים מרבי: 8

שלב 31: חיבורים ל- OV7670

על בלוק ov7670_axi_stream_capture

- הפוך את כל הכניסות לחיצוניות (קליק ימני על סיכה ובחר מהתפריט, או לחץ לחיצה שמאלית-> ctrl+T)

- השאר את השמות כפי שהם

על בלוק ov7670_controller

- הפוך את כל יציאות הבלוק לחיצוניות

- שנה את שם היציאה config_finished ל led0

- חבר את Clk ל- CameraClock (<= 50MHz) (FCLK_2)

על גוש ההדחה

- חבר את כניסת כפתור 1 ליציאת קלט חיצונית בשם btn0

- חבר את out1 לשורה השליחה מחדש בגוש ה- IP ov7670_controller

- חבר את כניסת button2 ליציאת קלט חיצונית בשם btn3

- חבר את out2n לכניסת ext_reset_in ב- IP איפוס מערכת המעבד עבור תחום שעון לכידת הווידאו. (*ייתכן שיהיה עליך לעשות זאת לאחר יצירת ה- IP*)

- חבר את Clk ל- CameraClock (<= 50MHz) (FCLK_2)

שלב 32: חיבורים בצד הווידאו החוצה

חיבורים לחסימות בקר תזמון וידאו (VTC), AXI4-Stream ל- Video Out ופרוסות

- השתמש בשעון 25MHz (FCLK_1) עבור vid_io_out_clk ו- VTC clk

- השתמש בשעון 100MHz (FCLK_0) עבור ACLK ב- AXI4-Stream ל- Video Out

- vtiming_out ל- vtiming_in

- מאגר מסגרת וידאו קרא m_axis_video עובר ל- AXI4-Stream ל- Video Out video_in

- vtg_ce עובר ל- gen_clken

- לקשור VTC clken, aclken, vid_io_out_ce ל- dout קבוע [0: 0]

- תביא vid_hsync ו- vid_vsync ליציאות הפלט החיצוניות vga_hs ו- vga_vs, בהתאמה. (לא בתמונה)

פרוסות:

-

יש להגדיר את הפרוסות כפי שמוצג בתמונות המצורפות

- שנה את שם הבלוקים ל- slice_red, slice_green ו- slice_blue

- טווחי פרוסת ההתקנה כפי שמוצג בתמונות לפי שם הבלוק

- חבר כל פלט פרוסה לפלט יציאה חיצונית כפי שמוצג בתמונה.

- vid_data [23: 0] מתחבר לכניסות לכל פרוסה (דין [23: 0])

שלב 33: הפעל אוטומציה של בלוק וחיבורים

הפעל את Block Automation כדי לחבר את הדברים מהבלוק ZYNQ7 PS. כפי שמוצג בתמונה.

הפעל את חיבור אוטומציה ליצירת כל ה- IP של קישוריות. שימו לב לכל האפשרויות בכל תמונה.

בגוש debounce, חבר את out2n לתחום השעון לכידת וידאו מעבד מערכת איפוס ext_reset_in.

שלב 34: צור עטיפת HDL

צור את עטיפת HDL לעיצוב הבלוק שלך.

הגדר אותו כמודול העליון.

שלב 35: צור Bitstream, ייצא חומרה ל- SDK, הפעל SDK מ- Vivado

הקפד לכלול את bitstream בייצוא.

ייצור של bitstream עשוי להימשך זמן רב מאוד.

לאחר מכן הפעל את SDK

שלב 36: SDK (ללא FreeRTOS)

גרסה זו עושה הכל מבלי להשתמש ב- FreeRTOS, ומעבה את הקוד בצורה יפה.

צור BSP עצמאי המבוסס על עיצוב החומרה. אפשרויות ברירת המחדל צריכות להיות בסדר. ודא שנוצרו מקורות BSP.

צור אפליקציה כפי שמוצג בתמונה. (יישום ריק)

מחק את הראשי שנוצר באופן אוטומטי וייבא את הקבצים המצורפים.

שלב 37: יישום FreeRTOS

גרסה זו אכן משתמשת ב- FreeRTOS. צור FreeRTOS901 BSP המבוסס על עיצוב החומרה. אפשרויות ברירת המחדל צריכות להיות בסדר. ודא שנוצרו מקורות BSP.

צור אפליקציה כפי שמוצג בתמונה. (יישום ריק)

מחק את הראשי שנוצר באופן אוטומטי וייבא את הקבצים המצורפים.

שלב 38: הוראות שימוש

הפרויקט הזה קצת מסובך להתחיל לפעול. בצע את השלבים לפי הסדר.

וודא ש- ZYBO שלך לא טוען דבר כאשר הוא מופעל. המשמעות היא ש- LED Done לא אמור להידלק. אחת הדרכים לעשות זאת היא להגדיר את מגשר מקור האתחול ל- JTAG.

פתח את הפרויקט (FreeRTOS או לא) שברצונך לתכנת מתוך SDK

- הפעל את ה- ZYBO שלך. נורית ה- Done לא אמורה להידלק.

- תכנת ה- FPGA עם קובץ הסיביות. נורית ה- Done אמורה להידלק. Led0 לא צריך להאיר.

- הפעל את הקוד (זכור לעבור את נקודת הפסקת ההתחלה אם אתה עושה זאת).

בשלב זה אתה אמור לקבל פלט על צג ה- VGA שלך.

כדי להפעיל מחדש (אם הוא באג או כל דבר אחר): הקש במהירות על כפתור PS-SRST או כבה את ה- ZYBO והפעל אותו שוב. המשך משלב 2.

עצירת המעבד באמצעות באגים תגרום למצלמה להחזיק בעמדה במקום לזוז. זרם הווידיאו ימשיך בכל מקרה.

שלב 39: הפניות וקישורים

מדריכי עיון ותיעוד של Xilinx:

- PG044 - AXI -Stream ל- Video Out

- PG278 - מאגר מסגרת וידאו קריאה/כתיבה

קישורים נוספים:

- הבלוג של לורי - קלט VDMA

- הבלוג של לורי - פלט OV7670 עד VGA באמצעות BRAM

- Wiki Hamsterworks מאת מייק פילדס, המקור המקורי של קוד OV7670

- גליון נתונים המציג מפרטי תזמון בסיסיים

מוּמלָץ:

פאן הטיה נשלט באמצעות טלפון סלולרי: 4 שלבים

פאן טילט הנשלט על ידי טלפון סלולרי: שלום לכולם, בפרויקט החדש הזה אציג בפניכם פאן-טילט הנשלט על ידי טלפון סלולרי. כל תנועות הטלפון הנייד משוכפלות במכשיר ההטה באמצעות Bluetooth. הבנייה היא מאוד פשוט באמצעות Arduino R3 (או דומה) ו- tw

מצלמת פטל PI וכוכב המוות בקרת אור: 5 שלבים (עם תמונות)

מצלמת פטל PI וכוכב המוות של בקרת אור: כמו תמיד אני מחפש לבנות מכשירים שימושיים, עובדים בצורה חזקה ולעתים קרובות הם אפילו שיפורים בהשוואה לפתרונות הנוכחיים מהמדף. הנה עוד פרויקט נהדר, שנקרא במקור Shadow 0f Phoenix, מגן פטל PI במשותף

מצלמת גיבוי של מצלמת מצלמה משופצת: 7 שלבים (עם תמונות)

מצלמת גיבוי מצלמת מצלמה: אני בטוח שלרובכם שקוראים זאת יש מגירה או ארון איפשהו מלא בטכנולוגיה אהובה שפשוט הזדקנה ומיושנת מדי. בהחלט יש לי את החלק שלי בטכנולוגיה הישנה, וזה עצוב לראות פוטנציאל כזה מתבזבז. ובכן, במדריך זה, אני ז

מנגנון פאן והטיה לחלוף זמן DSLR: 7 שלבים (עם תמונות)

מנגנון פאן והטיה לחלופי זמן DSLR: היו לי כמה מנועי צעד שוכבים ומאוד רציתי להשתמש בהם כדי להכין משהו מגניב. החלטתי שאכין מערכת פאן והטיה למצלמת ה- DSLR שלי כדי שאוכל ליצור חלופות זמן מגניבות. פריטים שתזדקק להם: 2x מנועי צעד -האט

התקנת מצלמת מצלמת CVS/ RiteAid ב- Zagi 400: 4 שלבים (עם תמונות)

התקנת מצלמת CVS/ RiteAid ב- Zagi 400: היה לי מצלמת חד פעמית מסוג CVS/ RiteAid מונחת זמן מה, אך לא ממש מצאתי בה שימוש עד כה, עד עכשיו. הסתובבתי ביוטיוב לפני כחודש וחיפשתי סרטוני מטוסים של RC ונתקלתי ב